# Quad 8-Bit CMOS D/A Converter with Internal 10 V Reference

**DAC-8426**

### 1.1 Scope.

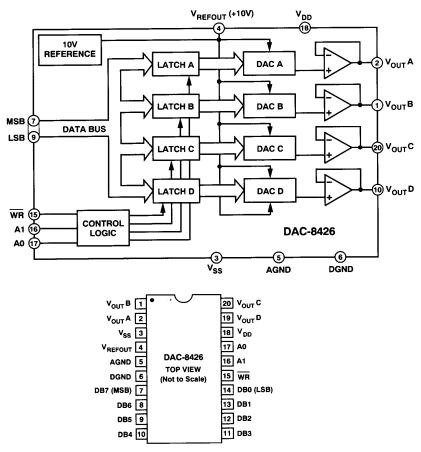

This specification covers the detail requirement for a quad 8-bit CMOS digital-to-analog converter with output voltage amplifiers and internal 10 V voltage reference. The internal latches provide direct interface for most microprocessors. The DAC-8426 operates with either a dual or single power supply.

It is highly recommended that this data sheet be used as a baseline for new military or aerospace specification control drawings.

#### 1.2 Part Number.

The complete part numbers per Table 1 of this specification is as follows:

Device Part Number Package

-1 DAC-8426AR/883 R

#### 1.2.3 Case Outline.

Letter Case Outline (Lead Finish per MIL-M-38510)

R 20-Lead Ceramic Dual-in-Line Package (Cerdip)

### 1.3 Absolute Maximum Ratings. $(T_A = +25^{\circ}C \text{ unless otherwise noted})$

| • \ n                                        |                                                                                                                                         |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> to AGND or DGND              | 0.3 V, +17 V                                                                                                                            |

| V <sub>SS</sub> to AGND or DGND              | $\cdots \cdots -7$ V, $V_{DD}$                                                                                                          |

| $V_{DD}$ to $V_{SS}$                         | $\cdots \cdots $ |

| AGND to DGND                                 | $\cdots \cdots -0.3 \text{ V}, +5 \text{ V}$                                                                                            |

| Digital Input Voltage to DGND                | $\dots \dots $                    |

| V <sub>REFOUT</sub> to AGND                  | $\cdots \cdots -0.3 \text{ V}, \text{ V}_{DD}$                                                                                          |

| V <sub>OUT</sub> to AGND                     | $V_{SS}$ , $V_{DD}$                                                                                                                     |

| Power Dissipation to +75°C                   | 500 mW                                                                                                                                  |

| Derate above 75°C by                         |                                                                                                                                         |

| Operating Temperature Range                  |                                                                                                                                         |

| Junction Temperature Range (T <sub>J</sub> ) | 65°C to +150°C                                                                                                                          |

| Storage Temperature Range                    | 65°C to +150°C                                                                                                                          |

| Lead Temperature (Soldering 60 sec)          | +300°C                                                                                                                                  |

|                                              |                                                                                                                                         |

#### 1.5 Thermal Characteristics.

Thermal Resistance  $\theta_{JC} = 7^{\circ}\text{C/W}$  $\theta_{JA} = 70^{\circ}\text{C/W max}$

## DAC-8426 — SPECIFICATIONS

Table 1.

|                                                          |                     | Device | Limits |       | Group A   |                                                                                                                   |       |

|----------------------------------------------------------|---------------------|--------|--------|-------|-----------|-------------------------------------------------------------------------------------------------------------------|-------|

| Test                                                     | Symbol              | Types  | Min    | Max   | Subgroups | Conditions <sup>1</sup>                                                                                           | Units |

| Resolution                                               | N                   | All    | 8      |       | 1, 2, 3   | $T_A = +25^{\circ}C, -55^{\circ}C \& +125^{\circ}C$                                                               | Bits  |

| Total Unadjusted Error                                   | TUE                 | -1     |        | ±1    | 1, 2, 3   | Includes Reference <sup>2</sup>                                                                                   | LSB   |

|                                                          |                     | -2     |        | ±2    | 1, 2, 3   | $T_A = +25^{\circ}C, -55^{\circ}C \& +125^{\circ}C$                                                               |       |

| Relative Accuracy                                        | INL                 | -1     |        | ±1/2  | 1, 2, 3   | $T_A = +25^{\circ}C, -55^{\circ}C \& +125^{\circ}C$                                                               | LSB   |

|                                                          |                     | -2     |        | ±1    | 1, 2, 3   |                                                                                                                   |       |

| Differential Nonlinearity                                | DNL                 | All    |        | ±1    | 1, 2, 3   | Note 3; $T_A = +25^{\circ}C$ , $-55^{\circ}C$ & $+125^{\circ}C$                                                   | LSB   |

| Zero Scale Error                                         | V <sub>ZSE</sub>    | All    |        | 20    | 1, 2, 3   | $V_{SS} = -5 \text{ V};$<br>$T_A = +25^{\circ}\text{C}, -55^{\circ}\text{C \& } +125^{\circ}\text{C}$             | mV    |

| Reference Output Voltage                                 | V <sub>REFOUT</sub> | -1     | 9.96   | 10.04 | 1, 2, 3   | No Load;                                                                                                          | V     |

|                                                          |                     | -2     | 9.92   | 10.08 |           | $T_A = +25^{\circ}C, -55^{\circ}C \& +125^{\circ}C$                                                               |       |

| Reference Load Regulation                                | $LD_{REG}$          | All    |        | 0.1   | 1, 2, 3   | $\Delta I_L = 10 \text{ mA};$<br>$T_A = +25^{\circ}\text{C}, -55^{\circ}\text{C \& } +125^{\circ}\text{C}$        | %/mA  |

| Reference Line Regulation                                | LN <sub>REG</sub>   | All    |        | 0.04  | 1, 2, 3   | $\Delta V_{DD} = \pm 10\%;$<br>$T_A = +25^{\circ}C, -55^{\circ}C \& +125^{\circ}C$                                | %/mA  |

| Reference Output Current                                 | I <sub>REFOUT</sub> | All    | 5      |       | 1, 2, 3   | $\Delta V_{REFOUT} < 40 \text{ mV};$<br>$T_A = +25^{\circ}\text{C}, -55^{\circ}\text{C \& } +125^{\circ}\text{C}$ |       |

| Logic Input "0"                                          | V <sub>INL</sub>    | All    |        | 0.8   | 1, 2, 3   | $T_A = +25^{\circ}C, -55^{\circ}C \& +125^{\circ}C$                                                               | V     |

| Logic Input "1"                                          | V <sub>INH</sub>    | All    | 2.4    |       | 1, 2, 3   | $T_A = +25^{\circ}C, -55^{\circ}C \& +125^{\circ}C$                                                               | V     |

| Logic Input Current                                      | I <sub>IN</sub>     | All    |        | 10    | 1, 2, 3   | $V_{IN} = 0 \text{ V or } V_{DD};$<br>$T_A = +25^{\circ}\text{C}, -55^{\circ}\text{C \& } +125^{\circ}\text{C}$   | μА    |

| Positive Supply Current <sup>3</sup>                     | $I_{DD}$            | All    |        | 14    | 1, 2, 3   | $T_A = +25^{\circ}C, -55^{\circ}C \& +125^{\circ}C$                                                               | mA    |

| Negative Supply Current <sup>3</sup>                     | I <sub>ss</sub>     | All    |        | 10    | 1, 2, 3   | Dual Supply, $V_{SS} = -5 \text{ V}$ ;<br>$T_A = +25^{\circ}\text{C}, -55^{\circ}\text{C} & +125^{\circ}\text{C}$ | mA    |

| Power Supply Sensitivity                                 | PSS                 | All    |        | 0.01  | 1, 2, 3   | $\Delta V_{DD} = \pm 10\%;$<br>$T_A = +25^{\circ}C, -55^{\circ}C \& +125^{\circ}C$                                | %/%   |

| Output Source Current                                    | I <sub>OUT</sub>    | All    | 10     |       | 1, 2, 3   | Digital Inputs All Ones;<br>T <sub>A</sub> = +25°C, -55°C & +125°C                                                | mA    |

| Output Sink Current                                      | I <sub>OUT</sub> -  | All    | 0.35   |       | 1, 2, 3   | Digital Inputs All Zeros                                                                                          | mA    |

| V <sub>OUT</sub> Settling Time<br>(Positive or Negative) | t <sub>S</sub>      | All    |        | 5     | 9         | To $\pm 1/2$ LSB; $T_A = +25^{\circ}C$                                                                            | μs    |

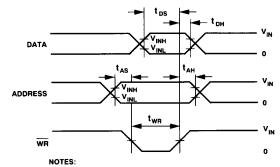

| Address to Write Setup Time                              | t <sub>AS</sub>     | All    | 0      |       | 9, 10, 11 | $T_A = +25^{\circ}C, -55^{\circ}C \& +125^{\circ}C$                                                               | ns    |

| Address to Write Hold Time                               | t <sub>AH</sub>     | All    | 0      |       | 9, 10, 11 | $T_A = +25^{\circ}C, -55^{\circ}C \& +125^{\circ}C$                                                               | ns    |

| Data Valid to Write Setup Time                           | t <sub>DS</sub>     | All    | 70     |       | 9, 10, 11 | $T_A = +25^{\circ}C, -55^{\circ}C \& +125^{\circ}C$                                                               | ns    |

| Data Valid to Write Hold Time                            | t <sub>DH</sub>     | All    | 10     |       | 9, 10, 11 | $T_A = +25^{\circ}C, -55^{\circ}C \& +125^{\circ}C$                                                               | ns    |

| Write Pulse Width                                        | t <sub>WR</sub>     | All    | 50     |       | 9, 10, 11 | $T_A = +25^{\circ}C, -55^{\circ}C \& +125^{\circ}C$                                                               | ns    |

| Minimum Load Resistance                                  | R <sub>L(MIN)</sub> | All    | 2      |       | 1, 2, 3   | Digital Inputs All Ones;<br>T <sub>A</sub> = +25°C, -55°C & +125°C                                                | kΩ    |

| V <sub>OUT</sub> Slew Rate                               | SR                  | All    | 2.5    |       | 7         | $T_A = +25^{\circ}C$                                                                                              | V/µs  |

NOTES  $^{1}V_{DD}=+15~V\pm10\%,~AGND=0~V,~DGND=0~V,~V_{SS}=0~V$  unless otherwise specified.  $^{2}Includes~full-scale~error,~relative~accuracy,~and~zero~code~error.$   $^{3}Digital~inputs~V_{IN}=V_{INL}~or~V_{INH};~V_{OUT}~and~V_{REFOUT}~unloaded.$

Table 2. Electrical Test Requirements for Class B Devices

| MIL-STD-883 Test Requirements               | Subgroups (See Table 3) |  |  |

|---------------------------------------------|-------------------------|--|--|

| Interim Electrical Parameters (Pre Burn-In) | 1                       |  |  |

| Final Electrical Test Parameters            | 1,* 2, 3                |  |  |

| Group A Test Requirements                   | 1, 2, 3, 7, 9, 10, 11   |  |  |

### NOTE

Table 3. Control Table

| Logi     | Logic Control WR A1 A0 |   | DAC-8426<br>Operation |  |  |

|----------|------------------------|---|-----------------------|--|--|

| WR       |                        |   |                       |  |  |

| H        | X                      | X | No Operation          |  |  |

|          |                        |   | Device Not Selected   |  |  |

| L        | L                      | L | DAC A Transparent     |  |  |

| <u>_</u> | L                      | L | DAC A Latched         |  |  |

| L        | L                      | Н | DAC B Transparent     |  |  |

| <u></u>  | L                      | Н | DAC B Latched         |  |  |

| L        | Н                      | L | DAC C Transparent     |  |  |

| <u>_</u> | Н                      | L | DAC C Latched         |  |  |

| L        | Н                      | Н | DAC D Transparent     |  |  |

| <u></u>  | Н                      | Н | DAC D Latched         |  |  |

L = Low State, H = High State, X = Don't Care.

- 1. ALL INPUT SIGNAL RISE AND FALL TIMES ARE MEASURED FROM THE 10% TO 90% OF  $V_{DD}$  ( $t_r = t_f = 20$ ns OVER THE  $V_{DD}$  RANGE)

- 2. TIMING REFERENCE LEVEL IS FROM V<sub>INH</sub> + V<sub>INL</sub>

3. V<sub>IN</sub> = 5V

Write Timing Diagram

<sup>\*</sup>PDA applies to Subgroup 1 only. No other subgroups are included in PDA.

### **DAC-8426**

### 3.2.1 Functional Block Diagram and Terminal Assignments.

### 3.2.4 Microcircuit Technology Group.

This microcircuit is covered by technology group 80.

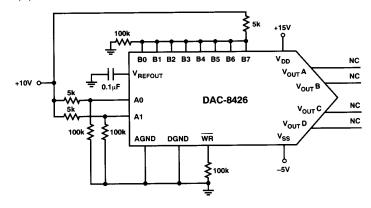

### 4.2.1 Life Test/Burn-In Circuit.

Steady state life test is per MIL-STD-883 Method 1005. Burn-in is per MIL-STD-883 Method 1015 test condition (B).

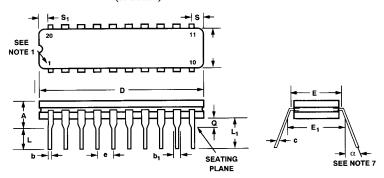

### 20-Lead Ceramic DIP

(R Suffix)

20-Lead Ceramic DIP (R Suffix)

|                | INCHES    |       | MILLIMETERS |       |       |

|----------------|-----------|-------|-------------|-------|-------|

| SYMBOL         | MIN       | MAX   | MIN         | MAX   | NOTES |

| Α              |           | 0.200 |             | 5.08  |       |

| b              | 0.014     | 0.023 | 0.36        | 0.58  |       |

| b <sub>1</sub> | 0.030     | 0.070 | 0.76        | 1.78  | 2     |

| С              | 0.008     | 0.015 | 0.20        | 0.38  |       |

| D              |           | 1.060 |             | 26.92 | 4     |

| E              | 0.220     | 0.310 | 5.59        | 7.87  | 4     |

| E <sub>1</sub> | 0.290     | 0.320 | 7.37        | 8.13  | 7     |

| е              | 0.100 BSC |       | 2.54 BSC    |       | 5     |

| L              | 0.125     | 0.200 | 3.18        | 5.08  |       |

| L <sub>1</sub> | 0.150     |       | 3.81        |       |       |

| a              | 0.015     | 0.060 | 0.38        | 1.52  | 3     |

| S              |           | 0.080 |             | 2.03  | 6     |

| Sı             | 0.005     |       | 0.13        |       | 6     |

| α              | 0°        | 15°   | 0°          | 15°   |       |

### NOTES

- 1. Index area; a notch or a lead one identification mark is located adjacent to lead one.

- The minimum limit for dimension b<sub>1</sub> may be 0.023" (0.58 mm) for all four corner leads only.

- 3. Dimension  ${\bf Q}$  shall be measured from the seating plane to the base plane.

- 4. This dimension allows for off-center lid, meniscus and glass overrun.

- 5. The basic lead spacing is 0.100" (2.54 mm) between centerlines.

- 6. Applies to all four corners.

- 7. Leads center when  $\alpha$  is 0°. E<sub>1</sub> shall be measured at the centerline of the leads.

### **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

### **Analog Devices Inc.:**

DAC8426FP DAC8426AR/883C DAC8426EPZ DAC8426FS DAC8426FPZ DAC8426FSZ