# GY Dual/Quad Low Noise, High Speed Precision Op Amps

## **FEATURES**

100% Tested Low Voltage Noise:

2.7nV/√Hz Typ 4.2nV/√Hz Max

■ Slew Rate: 4.5V/µs Typ

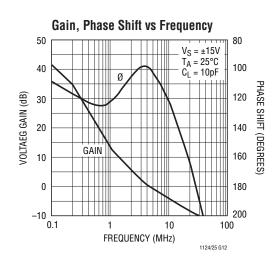

Gain-Bandwidth Product: 12.5MHz Typ

Offset Voltage,

Prime Grade: 70µV Max Low Grade: 100µV Max

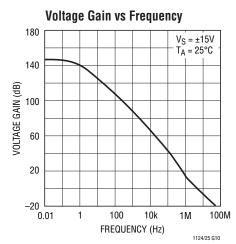

High Voltage Gain: 5 Million Min

Supply Current Per Amplifier: 2.75mA Max

Common Mode Rejection: 112dB MinPower Supply Rejection: 116dB Min

Available in 8-Pin SO Package

## **APPLICATIONS**

- Two and Three Op Amp Instrumentation Amplifiers

- Low Noise Signal Processing

- Active Filters

- Microvolt Accuracy Threshold Detection

- Strain Gauge Amplifiers

- Direct Coupled Audio Gain Stages

- Tape Head Preamplifiers

- Infrared Detectors

## DESCRIPTION

The LT®1124 dual and LT1125 quad are high performance op amps that offer higher gain, slew rate and bandwidth than the industry standard OP-27 and competing OP-270/OP-470 op amps. In addition, the LT1124/LT1125 have lower  $I_B$  and  $I_{OS}$  than the OP-27; lower  $V_{OS}$  and noise than the OP-270/OP-470.

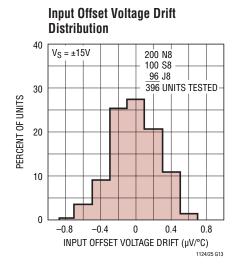

In the design, processing and testing of the device, particular attention has been paid to the optimization of the entire distribution of several key parameters. Slew rate, gain bandwidth and 1kHz noise are 100% tested for each individual amplifier. Consequently, the specifications of even the lowest cost grades (the LT1124C and the LT1125C) have been spectacularly improved compared to equivalent grades of competing amplifiers.

Power consumption of the LT1124 is one-half of two OP-27s. Low power and high performance in an 8-pin SO package make the LT1124 a first choice for surface mounted systems and where board space is restricted.

For a decompensated version of these devices, with three times higher slew rate and bandwidth, please see the LT1126/LT1127 data sheet.

ZT, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents including 4775884, 4837496.

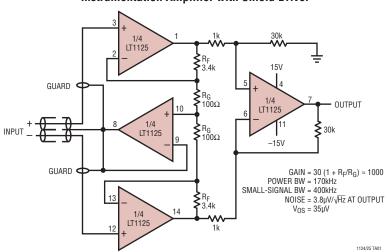

# TYPICAL APPLICATION

#### **Instrumentation Amplifier with Shield Driver**

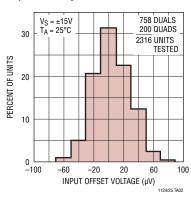

# Input Offset Voltage Distribution (All Packages, LT1124 and LT1125)

# **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| Supply Voltage                     | ±22V                    |

|------------------------------------|-------------------------|

| Input Voltages                     | Equal to Supply Voltage |

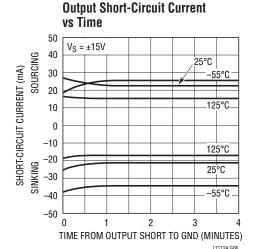

| Output Short-Circuit Duration      | Indefinite              |

| Differential Input Current (Note 6 | 6)±25mA                 |

| Lead Temperature (Soldering, 10    | sec)300°C               |

| Storage Temperature Range          | 65°C to 150°C           |

| Operating Temperature Range |                |

|-----------------------------|----------------|

| LT1124AC/LT1124C            |                |

| LT1125AC/LT1125C (Note 10)  | 40°C to 85°C   |

| LT1124AI/LT1124I            | 40°C to 85°C   |

| LT1124AMP/LT1125MP          | –55°C to 125°C |

| LT1124AM/LT1124M            |                |

| LT1125AM/LT1125M            |                |

| OBSOLETE                    | –55°C to 125°C |

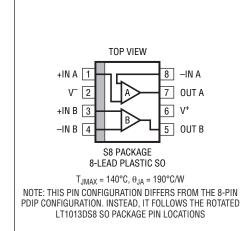

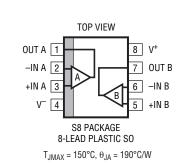

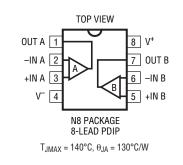

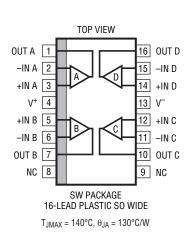

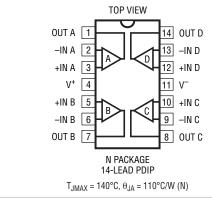

# PIN CONFIGURATION

#### **OBSOLETE PINOUT**

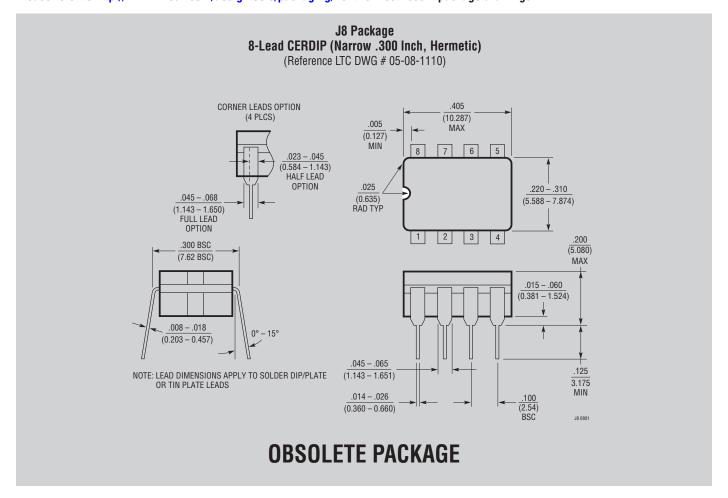

J8 PACKAGE 8-LEAD CERAMIC DIP  $T_{JMAX} = 160^{\circ}C, \, \theta_{JA} = 100^{\circ}C/W$

# **OBSOLETE PACKAGE**Consider the N8 for Alternate Source

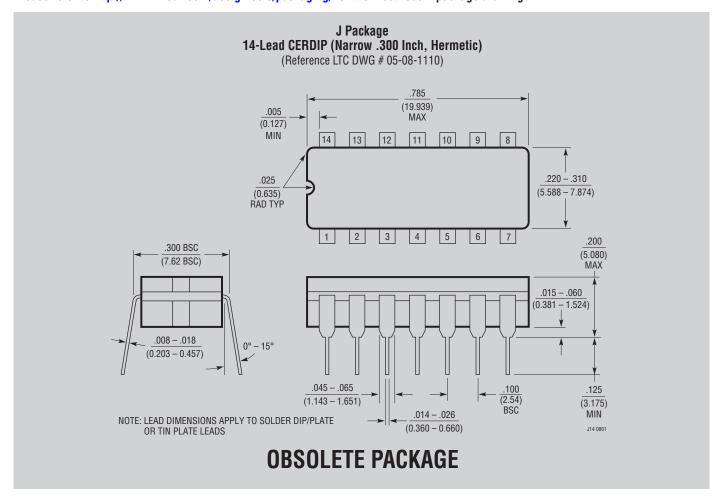

J PACKAGE 14-LEAD CERAMIC DIP T<sub>JMAX</sub> = 160°C, θ<sub>JA</sub> = 80°C/W

# **OBSOLETE PACKAGE**Consider the N for Alternate Source

# ORDER INFORMATION

| LEAD FREE FINISH  | TAPE AND REEL       | PART MARKING* | PACKAGE DESCRIPTION                | SPECIFIED TEMPERATURE RANGE |

|-------------------|---------------------|---------------|------------------------------------|-----------------------------|

| LT1124CS8#PBF     | LT1124CS8#TRPBF     | 1124          | 8-Lead Plastic SO, Rotated Pinout  | 0°C to 70°C                 |

| LT1124AIS8#PBF    | LT1124AIS8#TRPBF    | 1124AI        | 8-Lead Plastic SO, Rotated Pinout  | -40°C to 85°C               |

| LT1124IS8#PBF     | LT1124IS8#TRPBF     | 11241         | 8-Lead Plastic SO, Rotated Pinout  | -40°C to 85°C               |

| LT1124AMPS8#PBF   | LT1124AMPS8#TRPBF   | 124AMP        | 8-Lead Plastic SO, Rotated Pinout  | −55°C to 125°C              |

| LT1124CS8-1#PBF   | LT1124CS8-1#TRPBF   | 11241         | 8-Lead Plastic SO, Standard Pinout | 0°C to 70°C                 |

| LT1124AIS8-1#PBF  | LT1124AIS8-1#TRPBF  | 11241         | 8-Lead Plastic SO, Standard Pinout | -40°C to 85°C               |

| LT1124IS8-1#PBF   | LT1124IS8-1#TRPBF   | 11241         | 8-Lead Plastic SO, Standard Pinout | -40°C to 85°C               |

| LT1124AMPS8-1#PBF | LT1124AMPS8-1#TRPBF | 11241         | 8-Lead Plastic SO, Standard Pinout | -55°C to 125°C              |

|                   |                     | OBSOLET       | PINOUT                             |                             |

| LT1125CSW#PBF     | LT1125CSW#TRPBF     | LT1125CSW     | 16-Lead Plastic SO Wide            | 0°C to 70°C                 |

| LT1125MPSW        | LT1125MPSW#TR       | LT1125MPSW    | 16-Lead Plastic SO Wide            | −55°C to 125°C              |

| LT1124ACN8#PBF    | LT1124ACN8#TRPBF    | LT1124ACN8    | 8-Lead PDIP                        | 0°C to 70°C                 |

| LT1124CN8#PBF     | LT1124CN8#TRPBF     | LT1124CN8     | 8-Lead PDIP                        | 0°C to 70°C                 |

| LT1125ACN#PBF     | LT1125ACN#TRPBF     | LT1125ACN     | 14-Lead PDIP                       | 0°C to 70°C                 |

| LT1125CN#PBF      | LT1125CN#TRPBF      | LT1125CN      | 14-Lead PDIP                       | 0°C to 70°C                 |

| LEAD BASED FINISH | TAPE AND REEL       | PART MARKING* | PACKAGE DESCRIPTION                | SPECIFIED TEMPERATURE RANGE |

| LT1124CS8         | LT1124CS8#TR        | 1124          | 8-Lead Plastic SO, Rotated Pinout  | 0°C to 70°C                 |

| LT1124AIS8        | LT1124AIS8#TR       | 1124AI        | 8-Lead Plastic SO, Rotated Pinout  | -40°C to 85°C               |

| LT1124IS8         | LT1124IS8#TR        | 11241         | 8-Lead Plastic SO, Rotated Pinout  | -40°C to 85°C               |

| LT1125CSW         | LT1125CSW#TR        | LT1125CSW     | 16-Lead Plastic SO Wide            | 0°C to 70°C                 |

| LT1124ACN8        | LT1124ACN8#TR       | LT1124ACN8    | 8-Lead PDIP                        | 0°C to 70°C                 |

| LT1124CN8         | LT1124CN8#TR        | LT1124CN8     | 8-Lead PDIP                        | 0°C to 70°C                 |

| LT1125ACN         | LT1125ACN#TR        | LT1125ACN     | 14-Lead PDIP                       | 0°C to 70°C                 |

| LT1125CN          | LT1125CN#TR         | LT1125CN      | 14-Lead PDIP                       | 0°C to 70°C                 |

| LT1124CJ8         | LT1124CJ8#TR        | LT1124CJ8     | 8-Lead CERAMIC DIP                 | 0°C to 70°C                 |

| LT1124AMJ8        | LT1124AMJ8#TR       | LT1124AMJ8    | 8-Lead CERAMIC DIP                 | −55°C to 125°C              |

| LT1124MJ8         | LT1124MJ8#TR        | LT1124MJ8     | 8-Lead CERAMIC DIP                 | −55°C to 125°C              |

| LT1125CJ          | LT1125CJ#TR         | LT1125CJ      | 14-Lead CERAMIC DIP                | 0°C to 70°C                 |

| LT1125AMJ         | LT1125AMJ#TR        | LT1125AMJ     | 14-Lead CERAMIC DIP                | –55°C to 125°C              |

| LT1125MJ          | LT1125MJ#TR         | LT1125MJ      | 14-Lead CERAMIC DIP                | –55°C to 125°C              |

|                   |                     | OBSOLETE      | PACKAGE                            |                             |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** $T_A = 25^{\circ}C$ , $V_S = \pm 15V$ , unless otherwise noted.

|                                   |                                             |                                                                           | <b>I</b> | 124AC/A<br>1125AC/ | •          |            | T1124C/I<br>T1125C/ |            |                   |

|-----------------------------------|---------------------------------------------|---------------------------------------------------------------------------|----------|--------------------|------------|------------|---------------------|------------|-------------------|

| SYMBOL                            | PARAMETER                                   | CONDITIONS (Note 2)                                                       | MIN      | TYP                | MAX        | MIN        | TYP                 | MAX        | UNITS             |

| V <sub>OS</sub>                   | Input Offset Voltage                        | LT1124<br>LT1125                                                          |          | 20<br>25           | 70<br>90   |            | 25<br>30            | 100<br>140 | μV<br>μV          |

| $\Delta V_{OS} \over \Delta Time$ | Long-Term Input Offset<br>Voltage Stability |                                                                           |          | 0.3                |            |            | 0.3                 |            | μV/Mo             |

| I <sub>OS</sub>                   | Input Offset Current                        | LT1124<br>LT1125                                                          |          | 5<br>6             | 15<br>20   |            | 6<br>7              | 20<br>30   | nA<br>nA          |

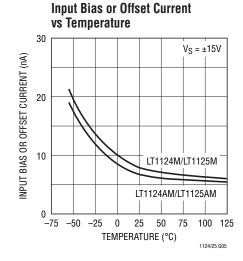

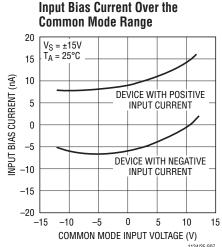

| I <sub>B</sub>                    | Input Bias Current                          |                                                                           |          | ±7                 | ±20        |            | ±8                  | ±30        | nA                |

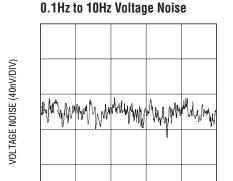

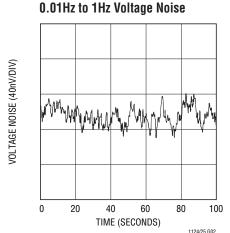

| e <sub>n</sub>                    | Input Noise Voltage                         | 0.1Hz to 10Hz (Notes 8, 9)                                                |          | 70                 | 200        |            | 70                  |            | nV <sub>P-P</sub> |

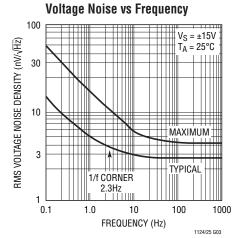

|                                   | Input Noise Voltage Density                 | f <sub>0</sub> = 10Hz (Note 5)<br>f <sub>0</sub> = 1000Hz (Note 3)        |          | 3.0<br>2.7         | 5.5<br>4.2 |            | 3.0<br>2.7          | 5.5<br>4.2 | nV/√Hz<br>nV/√Hz  |

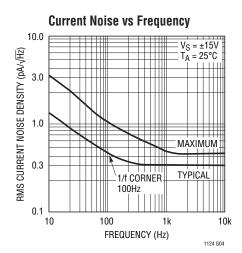

| i <sub>n</sub>                    | Input Noise Current Density                 | f <sub>0</sub> = 10Hz<br>f <sub>0</sub> = 1000Hz                          |          | 1.3<br>0.3         |            |            | 1.3<br>0.3          |            | pA/√Hz<br>pA/√Hz  |

| V <sub>CM</sub>                   | Input Voltage Range                         |                                                                           | ±12      | ±12.8              |            | ±12        | ±12.8               |            | V                 |

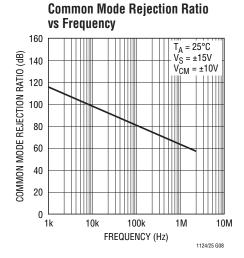

| CMRR                              | Common Mode Rejection Ratio                 | V <sub>CM</sub> = ±12V                                                    | 112      | 126                |            | 106        | 124                 |            | dB                |

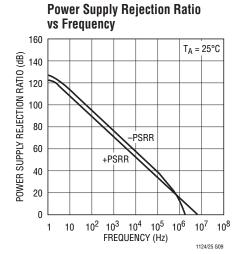

| PSRR                              | Power Supply Rejection Ratio                | $V_S = \pm 4V \text{ to } \pm 18V$                                        | 116      | 126                |            | 110        | 124                 |            | dB                |

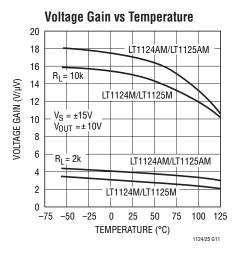

| A <sub>VOL</sub>                  | Large-Signal Voltage Gain                   | $R_L \ge 10k$ , $V_{OUT} = \pm 10V$<br>$R_L \ge 2k$ , $V_{OUT} = \pm 10V$ | 5<br>2   | 17<br>4            |            | 3.0<br>1.5 | 15<br>3             |            | V/μV<br>V/μV      |

| V <sub>OUT</sub>                  | Maximum Output Voltage Swing                | $R_L \ge 2k$                                                              | ±13      | ±13.8              |            | ±12.5      | ±13.8               |            | V                 |

| SR                                | Slew Rate                                   | $R_L \ge 2k \text{ (Notes 3, 7)}$                                         | 3        | 4.5                |            | 2.7        | 4.5                 |            | V/µs              |

| GBW                               | Gain-Bandwidth Product                      | f <sub>0</sub> = 100kHz (Note 3)                                          | 9        | 12.5               |            | 8          | 12.5                |            | MHz               |

| $\overline{Z_0}$                  | Open-Loop Output Resistance                 | $V_{OUT} = 0$ , $I_{OUT} = 0$                                             |          | 75                 |            |            | 75                  |            | Ω                 |

| Is                                | Supply Current per Amplifier                |                                                                           |          | 2.3                | 2.75       |            | 2.3                 | 2.75       | mA                |

|                                   | Channel Separation                          | $f \le 10$ Hz (Note 9)<br>$V_{OUT} = \pm 10$ V, $R_L = 2$ k               | 134      | 150                |            | 130        | 150                 |            | dB                |

The ullet denotes the specifications which apply over the  $-55^{\circ}C \leq T_{A} \leq 125^{\circ}C$  temperature range,  $V_{S} = \pm 15V$ , unless otherwise noted.

|                                     |                                       |                                                                                                         |   |        | T1124AI<br>T1125AI |            | l          | LT1124N<br>LT1125N |            |              |

|-------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------|---|--------|--------------------|------------|------------|--------------------|------------|--------------|

| SYMBOL                              | PARAMETER                             | CONDITIONS (Note 2)                                                                                     |   | MIN    | TYP                | MAX        | MIN        | TYP                | MAX        | UNITS        |

| V <sub>OS</sub>                     | Input Offset Voltage                  | LT1124<br>LT1125                                                                                        | • |        | 50<br>55           | 170<br>190 |            | 60<br>70           | 250<br>290 | μV<br>μV     |

| $\frac{\Delta V_{OS}}{\Delta Temp}$ | Average Input Offset<br>Voltage Drift | (Note 5)                                                                                                | • |        | 0.3                | 1.0        |            | 0.4                | 1.5        | μV/°C        |

| I <sub>OS</sub>                     | Input Offset Current                  | LT1124<br>LT1125                                                                                        | • |        | 18<br>18           | 45<br>55   |            | 20<br>20           | 60<br>70   | nA<br>nA     |

| I <sub>B</sub>                      | Input Bias Current                    |                                                                                                         | • |        | ±18                | ±55        |            | ±20                | ±70        | nA           |

| V <sub>CM</sub>                     | Input Voltage Range                   |                                                                                                         | • | ±11.3  | ±12                |            | ±11.3      | ±12                |            | V            |

| CMRR                                | Common Mode Rejection Ratio           | V <sub>CM</sub> = ±11.3V                                                                                | • | 106    | 122                |            | 100        | 120                |            | dB           |

| PSRR                                | Power Supply Rejection Ratio          | $V_S = \pm 4V \text{ to } \pm 18V$                                                                      | • | 110    | 122                |            | 104        | 120                |            | dB           |

| A <sub>VOL</sub>                    | Large-Signal Voltage Gain             | $\begin{aligned} R_L &\geq 10k, \ V_{OUT} = \pm 10V \\ R_L &\geq 2k, \ V_{OUT} = \pm 10V \end{aligned}$ | • | 3<br>1 | 10<br>3            |            | 2.0<br>0.7 | 10<br>2            |            | V/μV<br>V/μV |

| V <sub>OUT</sub>                    | Maximum Output Voltage Swing          | $R_L \ge 2k$                                                                                            | • | ±12.5  | ±13.6              |            | ±12        | ±13.6              |            | V            |

| SR                                  | Slew Rate                             | $R_L \ge 2k \text{ (Notes 3, 7)}$                                                                       | • | 2.3    | 3.8                |            | 2          | 3.8                |            | V/µs         |

| I <sub>S</sub>                      | Supply Current per Amplifier          |                                                                                                         | • |        | 2.5                | 3.25       |            | 2.5                | 3.25       | mA           |

11245f

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the spetemperature range, $V_S = \pm 15V$ , unless otherwise noted.

The  $\bullet$  denotes the specifications which apply over the  $0^{\circ}C \leq T_A \leq 70^{\circ}C$

|                                     |                                       |                                                                                                       |   |            |           |            |            | LT11240<br>LT11250 |            |              |

|-------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------|---|------------|-----------|------------|------------|--------------------|------------|--------------|

| SYMBOL                              | PARAMETER                             | CONDITIONS (Note 2)                                                                                   |   | MIN        | TYP       | MAX        | MIN        | TYP                | MAX        | UNITS        |

| V <sub>OS</sub>                     | Input Offset Voltage                  | LT1124<br>LT1125                                                                                      | • |            | 35<br>40  | 120<br>140 |            | 45<br>50           | 170<br>210 | μV<br>μV     |

| $\frac{\Delta V_{OS}}{\Delta Temp}$ | Average Input Offset<br>Voltage Drift | (Note 5)                                                                                              | • |            | 0.3       | 1          |            | 0.4                | 1.5        | μV/°C        |

| I <sub>OS</sub>                     | Input Offset Current                  | LT1124<br>LT1125                                                                                      | • |            | 6<br>7    | 25<br>35   |            | 7<br>8             | 35<br>45   | nA<br>nA     |

| I <sub>B</sub>                      | Input Bias Current                    |                                                                                                       | • |            | ±8        | ±35        |            | ±9                 | ±45        | nA           |

| V <sub>CM</sub>                     | Input Voltage Range                   |                                                                                                       | • | ±11.5      | ±12.4     |            | ±11.5      | ±12.4              |            | V            |

| CMRR                                | Common Mode Rejection Ratio           | V <sub>CM</sub> = ±11.5V                                                                              | • | 109        | 125       |            | 102        | 122                |            | dB           |

| PSRR                                | Power Supply Rejection Ratio          | $V_S = \pm 4V \text{ to } \pm 18V$                                                                    | • | 112        | 125       |            | 107        | 122                |            | dB           |

| A <sub>VOL</sub>                    | Large-Signal Voltage Gain             | $\begin{aligned} R_L &\geq 10k,  V_{OUT} = \pm 10V \\ R_L &\geq 2k,  V_{OUT} = \pm 10V \end{aligned}$ | • | 4.0<br>1.5 | 15<br>3.5 |            | 2.5<br>1.0 | 14<br>2.5          |            | V/μV<br>V/μV |

| V <sub>OUT</sub>                    | Maximum Output Voltage Swing          | $R_L \ge 2k$                                                                                          | • | ±12.5      | ±13.7     |            | ±12        | ±13.7              |            | V            |

| SR                                  | Slew Rate                             | R <sub>L</sub> ≥ 2k (Notes 3, 7)                                                                      | • | 2.6        | 4         |            | 2.4        | 4                  |            | V/µs         |

| I <sub>S</sub>                      | Supply Current per Amplifier          |                                                                                                       | • |            | 2.4       | 3          |            | 2.4                | 3          | mA           |

# The ullet denotes the specifications which apply over the $-40^{\circ}\text{C} \leq \text{T}_{A} \leq 85^{\circ}\text{C}$ temperature range, $\text{V}_{S} = \pm 15\text{V}$ , unless otherwise noted. (Note 10)

|                                     |                                       |                                                                                                       |   | 1          | 1124AC         |            | 1          | .T1124C        |            |              |

|-------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------|---|------------|----------------|------------|------------|----------------|------------|--------------|

| SYMBOL                              | PARAMETER                             | CONDITIONS (Note 2)                                                                                   |   | MIN L      | .T1125A<br>TYP | C<br>Max   | MIN        | LT11250<br>TYP | ;<br>Max   | UNITS        |

| V <sub>0S</sub>                     | Input Offset Voltage                  | LT1124<br>LT1125                                                                                      | • |            | 40<br>45       | 140<br>160 |            | 50<br>55       | 200<br>240 | μV<br>μV     |

| $\frac{\Delta V_{OS}}{\Delta Temp}$ | Average Input Offset<br>Voltage Drift | (Note 5)                                                                                              | • |            | 0.3            | 1          |            | 0.4            | 1.5        | μV/°C        |

| I <sub>OS</sub>                     | Input Offset Current                  | LT1124<br>LT1125                                                                                      | • |            | 15<br>15       | 40<br>50   |            | 17<br>17       | 55<br>65   | nA<br>nA     |

| I <sub>B</sub>                      | Input Bias Current                    |                                                                                                       | • |            | ±15            | ±50        |            | ±17            | ±65        | nA           |

| V <sub>CM</sub>                     | Input Voltage Range                   |                                                                                                       | • | ±11.4      | ±12.2          |            | ±11.4      | ±12.2          |            | V            |

| CMRR                                | Common Mode Rejection Ratio           | V <sub>CM</sub> = ±11.4V                                                                              | • | 107        | 124            |            | 101        | 121            |            | dB           |

| PSRR                                | Power Supply Rejection Ratio          | V <sub>S</sub> = ±4V to ±18V                                                                          | • | 111        | 124            |            | 106        | 121            |            | dB           |

| A <sub>VOL</sub>                    | Large-Signal Voltage Gain             | $\begin{aligned} R_L &\geq 10k,  V_{OUT} = \pm 10V \\ R_L &\geq 2k,  V_{OUT} = \pm 10V \end{aligned}$ | • | 3.5<br>1.2 | 12<br>3.2      |            | 2.2<br>0.8 | 12<br>2.3      |            | V/μV<br>V/μV |

| V <sub>OUT</sub>                    | Maximum Output Voltage Swing          | $R_L \ge 2k$                                                                                          | • | ±12.5      | ±13.6          |            | ±12        | ±13.6          |            | V            |

| SR                                  | Slew Rate                             | $R_L \ge 2k \text{ (Notes 3, 7)}$                                                                     | • | 2.4        | 3.9            |            | 2.1        | 3.9            |            | V/µs         |

| I <sub>S</sub>                      | Supply Current per Amplifier          |                                                                                                       | • |            | 2.4            | 3.25       |            | 2.4            | 3.25       | mA           |

## **ELECTRICAL CHARACTERISTICS**

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** Typical parameters are defined as the 60% yield of parameter distributions of individual amplifiers; i.e., out of 100 LT1125s (or 100 LT1124s) typically 240 op amps (or 120) will be better than the indicated specification.

Note 3: This parameter is 100% tested for each individual amplifier.

**Note 4:** This parameter is sample tested only.

Note 5: This parameter is not 100% tested.

**Note 6:** The inputs are protected by back-to-back diodes. Current limiting resistors are not used in order to achieve low noise. If differential input

voltage exceeds ±1.4V, the input current should be limited to 25mA.

Note 7: Slew rate is measured in  $A_V = -1$ ; input signal is  $\pm 7.5V$ , output measured at  $\pm 2.5V$ .

**Note 8:** 0.1Hz to 10Hz noise can be inferred from the 10Hz noise voltage density test. See the test circuit and frequency response curve for 0.1Hz to 10Hz tester in the Applications Information section of the LT1007 or LT1028 data sheets.

**Note 9:** This parameter is guaranteed but not tested.

**Note 10:** The LT1124C/LT1125C and LT1124AC/LT1125AC are guaranteed to meet specified performance from 0°C to 70°C and are designed, characterized and expected to meet these extended temperature limits, but are not tested at –40°C and 85°C. The LT1124AI and LT1124I are guaranteed to meet the extended temperature limits.

## TYPICAL PERFORMANCE CHARACTERISTICS

4

6

TIME (SECONDS)

8

10

1124/25 G01

0

# TYPICAL PERFORMANCE CHARACTERISTICS

# TYPICAL PERFORMANCE CHARACTERISTICS

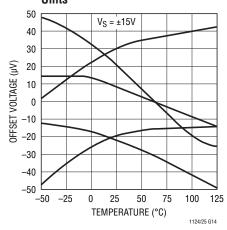

Offset Voltage Drift with Temperature of Representative Units

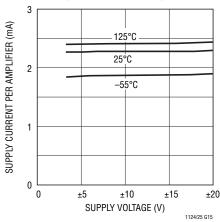

**Supply Current vs Supply Voltage**

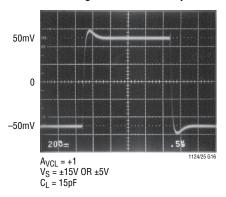

Small-Signal Transient Response

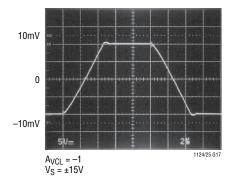

**Large-Signal Transient Response**

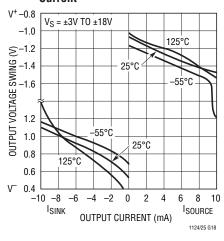

Output Voltage Swing vs Load Current

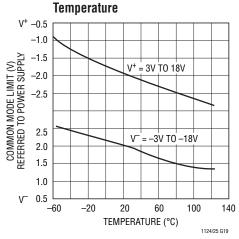

Common Mode Limit vs

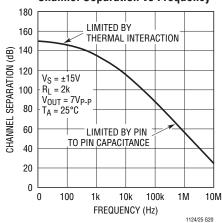

Channel Separation vs Frequency

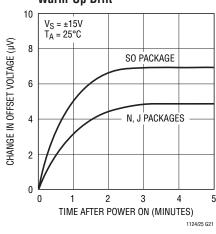

#### Warm-Up Drift

# TYPICAL PERFORMANCE CHARACTERISTICS

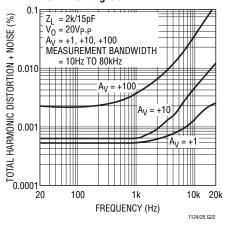

#### Total Harmonic Distortion and Noise vs Frequency for Noninverting Gain

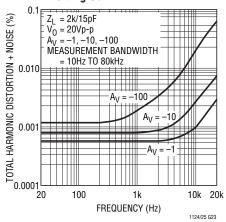

#### Total Harmonic Distortion and Noise vs Frequency for Inverting Gain

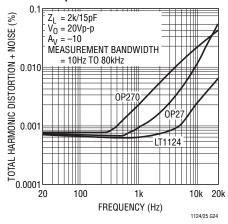

Total Harmonic Distortion and Noise vs Frequency for Competitive Devices

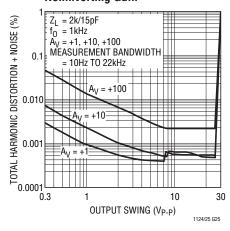

#### Total Harmonic Distortion and Noise vs Output Amplitude for Noninverting Gain

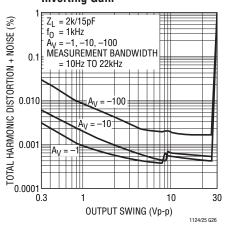

Total Harmonic Distortion and Noise vs Output Amplitude for Inverting Gain

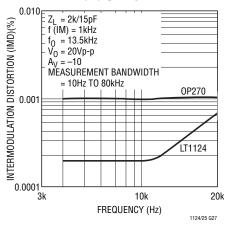

Intermodulation Distortion (CCIF Method)\* vs Frequency LT1124 and OP270

## APPLICATIONS INFORMATION

The LT1124 may be inserted directly into OP-270 sockets. The LT1125 plugs into OP-470 sockets. Of course, all standard dual and quad bipolar op amps can also be replaced by these devices.

#### **Matching Specifications**

In many applications the performance of a system depends on the matching between two op amps, rather than the individual characteristics of the two devices. The three op amp instrumentation amplifier configuration shown in this data sheet is an example. Matching characteristics are not 100% tested on the LT1124/LT1125.

Some specifications are guaranteed by definition. For example,  $70\mu V$  maximum offset voltage implies that mismatch cannot be more than  $140\mu V$ . 112dB (=  $2.5\mu V/V$ ) CMRR means that worst-case CMRR match is 106dB

$(5\mu V/V)$ . However, Table 1 can be used to estimate the expected matching performance between the two sides of the LT1124, and between amplifiers A and D, and between amplifiers B and C of the LT1125.

#### Offset Voltage and Drift

Thermocouple effects, caused by temperature gradients across dissimilar metals at the contacts to the input terminals, can exceed the inherent drift of the amplifier unless proper care is exercised. Air currents should be minimized, package leads should be short, the two input leads should be close together and maintained at the same temperature.

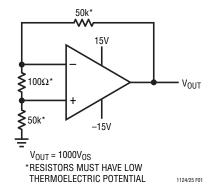

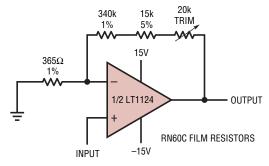

The circuit shown in Figure 1 to measure offset voltage is also used as the burn-in configuration for the LT1124/LT1125, with the supply voltages increased to ±16V.

Figure 1. Test Circuit for Offset Voltage and Offset Voltage Drift with Temperature

Table 1. Expected Match

|                                         |                  |           | LT1124AC/AM<br>LT1125AC/AM |           | LT1124C/M<br>LT1125C/M |       |  |

|-----------------------------------------|------------------|-----------|----------------------------|-----------|------------------------|-------|--|

| PARAMETER                               |                  | 50% YIELD | 98% YIELD                  | 50% YIELD | 98% YIELD              | UNITS |  |

| V <sub>OS</sub> Match, ΔV <sub>OS</sub> | LT1124           | 20        | 110                        | 30        | 130                    | μV    |  |

|                                         | LT1125           | 30        | 150                        | 50        | 180                    | μV    |  |

| Temperature Coeffici                    | ient Match       | 0.35      | 1.0                        | 0.5       | 1.5                    | μV/°C |  |

| Average Noninvertin                     | g I <sub>B</sub> | 6         | 18                         | 7         | 25                     | nA    |  |

| Match of Noninverting I <sub>B</sub>    |                  | 7         | 22                         | 8         | 30                     | nA    |  |

| CMRR Match                              |                  | 126       | 115                        | 123       | 112                    | dB    |  |

| PSRR Match                              |                  | 127       | 118                        | 127       | 114                    | dB    |  |

/ LINEAR

## APPLICATIONS INFORMATION

#### **High Speed Operation**

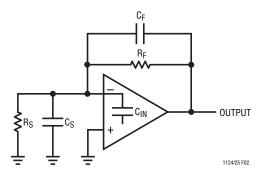

When the feedback around the op amp is resistive ( $R_F$ ), a pole will be created with  $R_F$ , the source resistance and capacitance ( $R_S$ ,  $C_S$ ), and the amplifier input capacitance ( $C_{IN} \approx 2pF$ ). In low closed loop gain configurations and with  $R_S$  and  $R_F$  in the kilohm range, this pole can create excess phase shift and even oscillation. A small capacitor ( $C_F$ ) in parallel with  $R_F$  eliminates this problem (see Figure 2). With  $R_S$  ( $C_S + C_{IN}$ ) =  $R_F C_F$ , the effect of the feedback pole is completely removed.

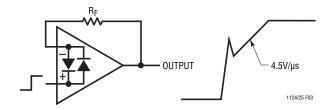

Figure 2. High Speed Operation

## **Unity Gain Buffer Applications**

When  $R_F \le 100\Omega$  and the input is driven with a fast, large signal pulse (>1V), the output waveform will look as shown in Figure 3.

Figure 3. Unity-Gain Buffer Applications

During the fast feedthrough-like portion of the output, the input protection diodes effectively short the output to the input and a current, limited only by the output short circuit protection, will be drawn by the signal generator. With  $R_F \!\ge\! 500\Omega$ , the output is capable of handling the current requirements (I<sub>L</sub>  $\le 20\text{mA}$  at 10V) and the amplifier stays in its active mode and a smooth transition will occur.

#### **Noise Testing**

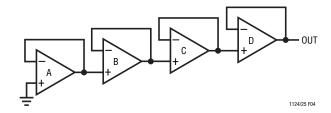

Each individual amplifier is tested to  $4.2\text{nV}/\sqrt{\text{Hz}}$  voltage noise; i.e., for the LT1124 two tests, for the LT1125 four tests are performed. Noise testing for competing multiple op amps, if done at all, may be sample tested or tested using the circuit shown in Figure 4.

$$e_{n \text{ OUT}} = \sqrt{(e_{nA})^2 + (e_{nB})^2 + (e_{nC})^2 + (e_{nD})^2}$$

If the LT1125 were tested this way, the noise limit would be  $\sqrt{4 \cdot (4.2 \text{nV}/\sqrt{\text{Hz}})^2} = 8.4 \text{nV}/\sqrt{\text{Hz}}$ . But is this an effective screen? What if three of the four amplifiers are at a typical  $2.7 \text{nV}/\sqrt{\text{Hz}}$ , and the fourth one was contaminated and has  $6.9 \text{nV}/\sqrt{\text{Hz}}$  noise?

RMS Sum =

$$\sqrt{(2.7)^2 + (2.7)^2 + (2.7)^2 + (6.9)^2}$$

= 8.33nV/ $\sqrt{\text{Hz}}$

This passes an  $8.4\text{nV}/\sqrt{\text{Hz}}$  spec, yet one of the amplifiers is 64% over the LT1125 spec limit. Clearly, for proper noise measurement, the op amps have to be tested individually.

Figure 4. Competing Quad Op Amp Noise Test Method

## PERFORMANCE COMPARISON

Table 2 summarizes the performance of the LT1124/LT1125 compared to the low cost grades of alternate approaches.

The comparison shows how the specs of the LT1124/LT1125 not only stand up to the industry standard OP-27, but in most cases are superior. Normally dual and quad

performance is degraded when compared to singles, for the LT1124/LT1125 this is not the case.

Table 2. Guaranteed Performance,  $V_S = \pm 15V$ ,  $T_A = 25^{\circ}C$ , Low Cost Devices

| PARAMETER/UN                      | ITS              | LT1124CN8<br>LT1125CN | OP-27 GP             | 0P-270 GP     | OP-470 GP            | UNITS    |

|-----------------------------------|------------------|-----------------------|----------------------|---------------|----------------------|----------|

| Voltage Noise, 1k                 | (Hz              | 4.2<br>100% Tested    | 4.5<br>Sample Tested | –<br>No Limit | 5.0<br>Sample Tested | nV/√Hz   |

| Slew Rate                         |                  | 2.7<br>100% Tested    | 1.7<br>Not Tested    | 1.7           | 1.4                  | V/µs     |

| Gain-Bandwidth                    | Product          | 8.0<br>100% Tested    | 5.0<br>Not Tested    | –<br>No Limit | –<br>No Limit        | MHz      |

| Offset Voltage                    | LT1124<br>LT1125 | 100<br>140            | 100<br>-             | 250<br>-      | -<br>1000            | μV<br>μV |

| Offset Current                    | LT1124<br>LT1125 | 20<br>30              | 75<br>-              | 20<br>-       | -<br>30              | nA<br>nA |

| Bias Current                      |                  | 30                    | 80                   | 60            | 60                   | nA       |

| Supply Current/A                  | mp               | 2.75                  | 5.67                 | 3.25          | 2.75                 | mA       |

| Voltage Gain, R <sub>L</sub> = 2k |                  | 1.5                   | 0.7                  | 0.35          | 0.4                  | V/µV     |

| Common Mode Rejection Ratio       |                  | 106                   | 100                  | 90            | 100                  | dB       |

| Power Supply Rejection Ratio      |                  | 110                   | 94                   | 104           | 105                  | dB       |

| SO-8 Package                      |                  | Yes – LT1124          | Yes                  | No            | -                    |          |

# TYPICAL APPLICATIONS

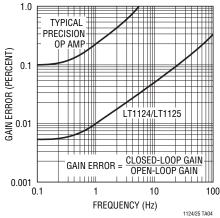

Gain 1000 Amplifier with 0.01% Accuracy, DC to 1Hz

THE HIGH GAIN AND WIDE BANDWIDTH OF THE LT1124/LT1125, IS USEFUL IN LOW FREQUENCY HIGH CLOSED-LOOP GAIN AMPLIFIER APPLICATIONS. A TYPICAL PRECISION OP AMP MAY HAVE AN OPEN-LOOP GAIN OF ONE MILLION WITH 500kHz BANDWIDTH. AS THE GAIN ERROR PLOT SHOWS, THIS DEVICE IS CAPABLE OF 0.1% AMPLIFYING ACCURACY UP TO 0.3Hz ONLY. EVEN INSTRUMENTATION RANGE SIGNALS CAN VARY AT A FASTER RATE. THE LT1124/LT1125 "GAIN PRECISION — BANDWIDTH PRODUCT" IS 75 TIMES HIGHER, AS SHOWN.

Gain Error vs Frequency Closed-Loop Gain = 1000

11245ff

1124/25 TA03

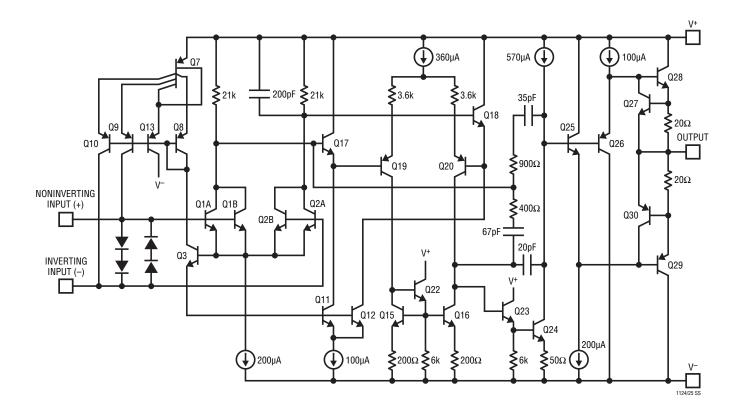

# SCHEMATIC DIAGRAM (1/2 LT1124, 1/4 LT1125)

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

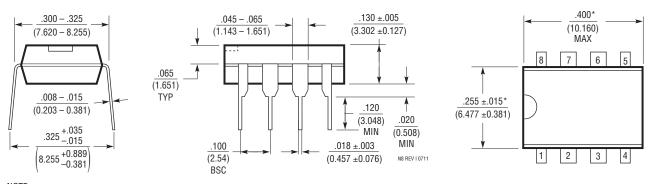

#### N8 Package 8-Lead PDIP (Narrow .300 Inch)

(Reference LTC DWG # 05-08-1510 Rev I)

NOTE: 1. DIMENSIONS ARE MILLIMETERS

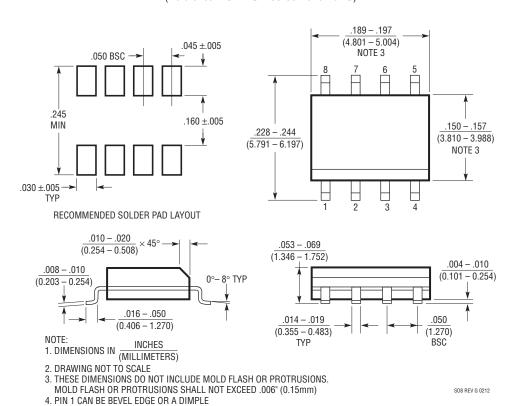

#### \$8 Package 8-Lead Plastic Small Outline (Narrow .150 Inch)

(Reference LTC DWG # 05-08-1610 Rev G)

/ LINEAR

<sup>\*</sup>THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .010 INCH (0.254mm)

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

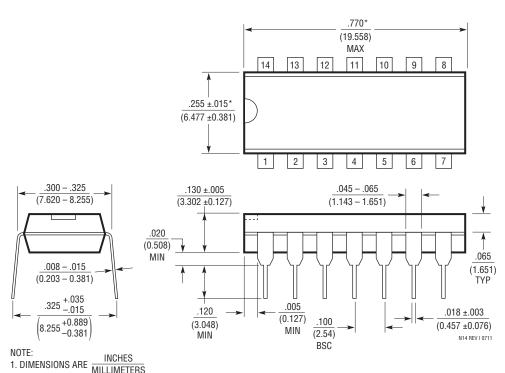

#### N Package 14-Lead PDIP (Narrow .300 Inch)

(Reference LTC DWG # 05-08-1510 Rev I)

DIMENSIONS ARE INCHES

MILLIMETERS

\*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .010 INCH (0.254mm)

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

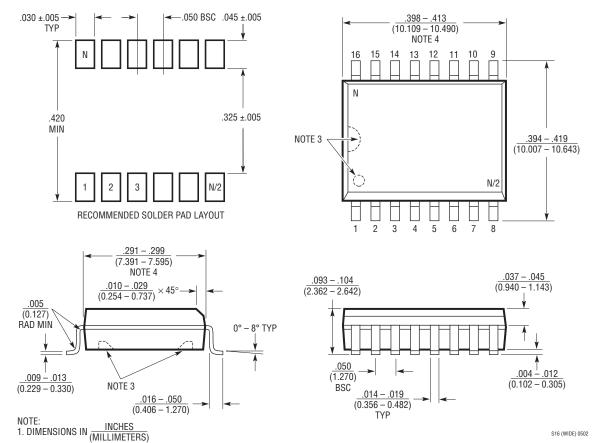

#### SW Package 16-Lead Plastic Small Outline (Wide .300 Inch)

(Reference LTC DWG # 05-08-1620)

- 2. DRAWING NOT TO SCALE

- PIN 1 IDENT, NOTCH ON TOP AND CAVITIES ON THE BOTTOM OF PACKAGES ARE THE MANUFACTURING OPTIONS. THE PART MAY BE SUPPLIED WITH OR WITHOUT ANY OF THE OPTIONS

- 4. THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .006" (0.15mm)

# **REVISION HISTORY** (Revision history begins at Rev D)

| REV | DATE                                                                       | DESCRIPTION       | PAGE NUMBER |  |  |

|-----|----------------------------------------------------------------------------|-------------------|-------------|--|--|

| D   | 09/10 LT1124-1 added. Reflected throughout the data sheet.                 |                   |             |  |  |

| Е   | 10/10 Revised part marking for LT1124AMPS8-1 in Order Information section. |                   |             |  |  |

| F   | 01/14                                                                      | LT1124-1 removed. | 1 to 3      |  |  |

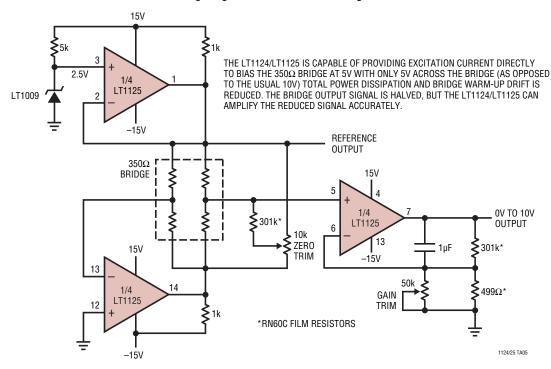

# TYPICAL APPLICATION

#### Strain Gauge Signal Conditioner with Bridge Excitation

# **RELATED PARTS**

| PART NUMBER   | DESCRIPTION                         | COMMENTS                                                              |

|---------------|-------------------------------------|-----------------------------------------------------------------------|

| LT1007        | Single Low Noise, Precision Op Amp  | 2.5nV/√Hz 1kHz Voltage Noise                                          |

| LT1028/LT1128 | Single Low Noise, Precision Op Amps | 0.85nV/√Hz Voltage Noise                                              |

| LT1112/LT1114 | Dual/Quad Precision Picoamp Input   | 250pA Max I <sub>B</sub>                                              |

| LT1113        | Dual Low Noise JFET Op Amp          | 4.5nV/√Hz Voltage Noise, 10fA/√Hz Current Noise                       |

| LT1126/LT1127 | Decompensated LT1124/LT1125         | 11V/µs Slew Rate                                                      |

| LT1169        | Dual Low Noise JFET Op Amp          | 6nV/√Hz Voltage Noise, 1fA/√Hz Current Noise, 10pA Max I <sub>B</sub> |

| LT1792        | Single LT1113                       | 4.2nV/√Hz Voltage Noise, 10fA/√Hz Current Noise                       |

| LT1793        | Single LT1169                       | 6nV/√Hz Voltage Noise, 1fA/√Hz Current Noise, 10pA Max I <sub>B</sub> |

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# **Analog Devices Inc.:**

LT1124IS8#PBF LT1125MPSW#PBF LT1124ACN8#PBF LT1124CS8#TRPBF LT1125ACN#PBF LT1124CS8#PBF LT1125CSW#PBF LT1124AMPS8#PBF LT1125CSW#TRPBF LT1124AIS8#TRPBF LT1124CN8#PBF LT1125CSW#TRPBF LT1124IS8#TRPBF LT1124AIS8#TRPBF LT1124CN8#PBF LT1125MPSW#TRPBF