Micropower

High Output Current

Step-Up Adjustable and

Fixed 5V DC/DC Converters

### **FEATURES**

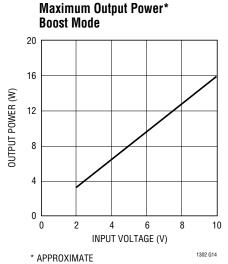

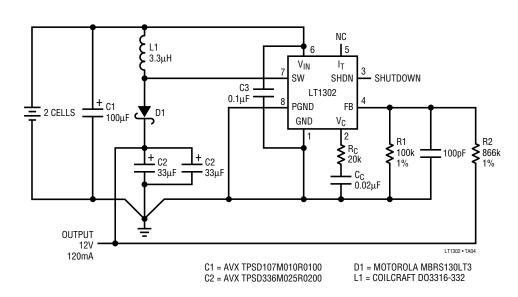

- 5V at 600mA or 12V at 120mA from 2-Cell Supply

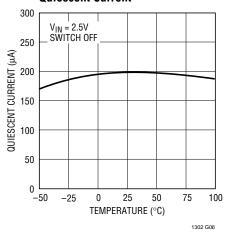

- 200µA Quiescent Current

- Logic Controlled Shutdown to 15µA

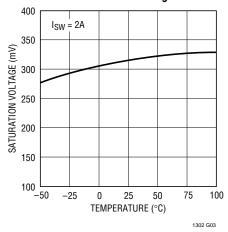

- Low V<sub>CESAT</sub> Switch: 310mV at 2A Typical

- Burst Mode<sup>™</sup> Operation at Light Load

- Current Mode Operation for Excellent Line and Load Transient Response

- Available in 8-Lead SO or PDIP

- Operates with Supply Voltage as Low as 2V

### **APPLICATIONS**

- Notebook and Palmtop Computers

- Portable Instruments

- Personal Digital Assistants

- Cellular Telephones

- Flash Memory

### DESCRIPTION

The LT®1302/LT1302-5 are micropower step-up DC/DC converters that maintain high efficiency over a wide range of output current. They operate from a supply voltage as low as 2V and feature automatic shifting between Burst Mode operation at light load, and current mode operation at heavy load.

The internal low loss NPN power switch can handle current in excess of 2A and switch at frequencies up to 400kHz. Quiescent current is just  $200\mu A$  and can be further reduced to  $15\mu A$  in shutdown.

Available in 8-pin PDIP or 8-pin SO packaging, the LT1302/LT1302-5 have the highest switch current rating of any similarly packaged switching regulators presently on the market.

**LT**, LTC and LT are registered trademarks of Linear Technology Corporation. Burst Mode is a trademark of Linear Technology Corporation.

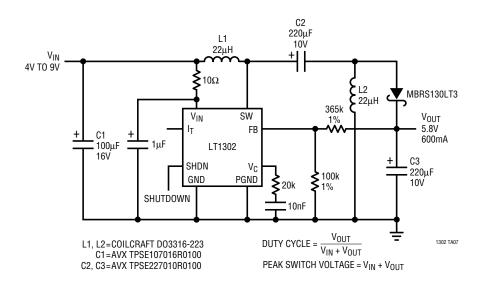

### TYPICAL APPLICATION

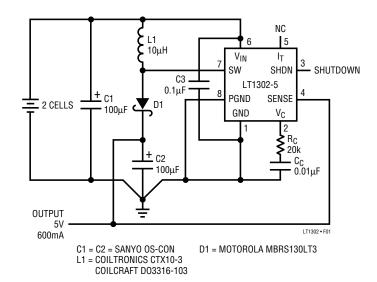

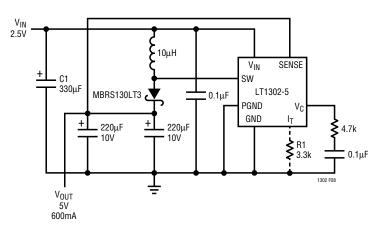

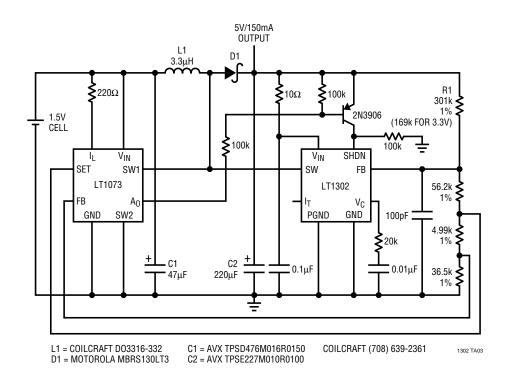

Figure 1. 2-Cell to 5V/600mA DC/DC Converter

#### 90 88 86 84 $V_{IN} = 2.5V$ EFFICIENCY (%) 82 80 78 76 74 72 70 10 100 1000 LOAD CURRENT (mA) LT1302 • TA02

2-Cell to 5V Converter Efficiency

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>IN</sub> Voltage1                 |     |

|------------------------------------------|-----|

| SW Voltage 2                             | 25V |

| FB Voltage 1                             | .0V |

| SHDN Voltage 1                           | 0V  |

| V <sub>C</sub> Voltage                   | 4V  |

| I <sub>T</sub> Voltage                   | 4V  |

| Maximum Power Dissipation 700n           | nW  |

| Operating Temperature Range 0°C to 70    | )°C |

| Storage Temperature Range65°C to 150     | )°C |

| Lead Temperature (Soldering, 10 sec) 300 | )°C |

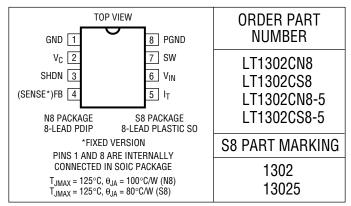

### PACKAGE/ORDER INFORMATION

Consult factory for Industrial and Military grade parts.

# DC ELECTRICAL CHARACTERISTICS $T_A = 25$ °C, $V_{IN} = 2.5$ V, unless otherwise noted.

| SYMBOL             | PARAMETER                                 | CONDITIONS                                                                   |   | MIN        | TYP       | MAX        | UNITS      |

|--------------------|-------------------------------------------|------------------------------------------------------------------------------|---|------------|-----------|------------|------------|

| IQ                 | Quiescent Current                         | V <sub>SHDN</sub> = 0.5V, V <sub>FB</sub> = 1.3V<br>V <sub>SHDN</sub> = 1.8V | • |            | 200<br>15 | 300<br>25  | μA<br>μA   |

| V <sub>IN</sub>    | Input Voltage Range                       |                                                                              | • | 2.0<br>2.2 |           | 8          | V          |

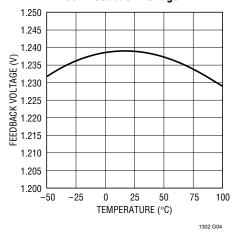

| V <sub>FB</sub>    | Feedback Voltage (LT1302)                 | $V_C = 0.4V$                                                                 | • | 1.22       | 1.24      | 1.26       | V          |

|                    | Feedback Pin Bias Current (LT1302)        | V <sub>FB</sub> = 1V                                                         |   |            | 100       |            | nA         |

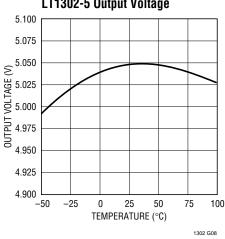

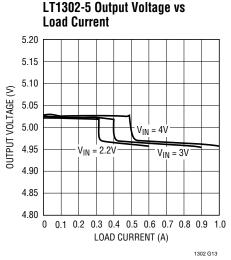

|                    | Output Sense Voltage (LT1302-5)           | V <sub>C</sub> = 0.4V                                                        | • | 4.85       | 5.05      | 5.25       | V          |

|                    | Output Ripple Voltage (LT1302-5)          | V <sub>C</sub> = 0.4V                                                        |   |            | 50        |            | mV         |

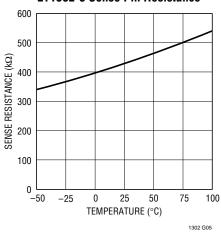

|                    | Sense Pin Resistance to Ground (LT1302-5) |                                                                              |   |            | 420       |            | kΩ         |

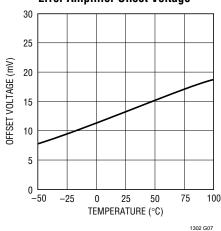

| $V_{OS}$           | Offset Voltage                            | See Block Diagram                                                            |   |            | 15        |            | mV         |

|                    | Comparator Hysteresis                     | (Note 1)                                                                     |   |            | 5         |            | mV         |

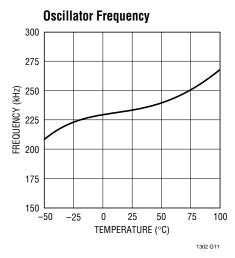

|                    | Oscillator Frequency                      | Current Limit Not Asserted (Note 2)                                          | • | 175<br>160 | 220       | 265<br>310 | kHz<br>kHZ |

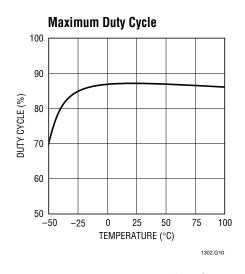

| DC                 | Maximum Duty Cycle                        |                                                                              |   | 75         | 86        | 95         | %          |

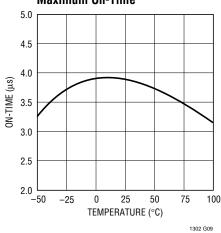

| $t_{ON}$           | Switch On Time                            | Current Limit Not Asserted                                                   |   |            | 3.9       |            | μS         |

| t <sub>OFF</sub>   | Switch Off Time                           |                                                                              |   |            | 0.7       |            | μS         |

|                    | Output Line Regulation                    | 2 < V <sub>IN</sub> < 8V                                                     | • |            | 0.06      | 0.15       | %/V        |

| V <sub>CESAT</sub> | Switch Saturation Voltage                 | I <sub>SW</sub> = 2A                                                         | • |            | 310       | 400<br>475 | mV<br>mV   |

|                    | Switch Leakage Current                    | V <sub>SW</sub> = 5V, Switch Off                                             | • |            | 0.1       | 10         | μА         |

|                    | Switch Current Limit                      | V <sub>C</sub> = 0.4V (Burst Mode Operation)                                 |   |            | 1         |            | А          |

|                    |                                           | $V_C = 1.25V$ (Full Power) (Note 3)                                          | • | 2.0        | 2.8       | 3.9        | A          |

|                    | Error Amplifier Voltage Gain              | $0.9V \le V_C \le 1.2V$ , $\Delta V_C/\Delta V_{FB}$                         |   | 50         | 75        |            | V/V        |

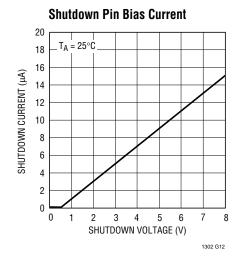

| $V_{SHDNH}$        | Shutdown Pin High                         |                                                                              | • | 1.8        |           |            | V          |

| $V_{SHDNL}$        | Shutdown Pin Low                          |                                                                              | • |            |           | 0.5        | V          |

| I <sub>SHDN</sub>  | Shutdown Pin Bias Current                 | $V_{SHDN} = 5V$                                                              | • |            | 8         | 20         | μА         |

|                    |                                           | V <sub>SHDN</sub> = 2V                                                       |   |            | 3         |            | μA         |

|                    |                                           | V <sub>SHDN</sub> = 0V                                                       | • |            | 0.1       | 1          | μA         |

|                    | I <sub>T</sub> Pin Resistance to Ground   |                                                                              |   |            | 3.9       |            | kΩ         |

The ● denotes specifications which apply over the 0°C to 70°C temperature range.

**Note 1:** Hysteresis is specified at DC. Output ripple depends on capacitor size and ESR.

**Note 2:** The LT1302 operates in a variable frequency mode. Switching frequency depends on load inductance and operating conditions and may be above specified limits.

**Note 3:** Minimum switch current 100% tested. Maximum switch current guaranteed by design.

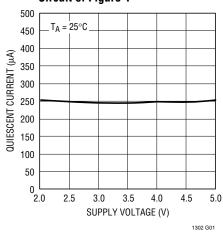

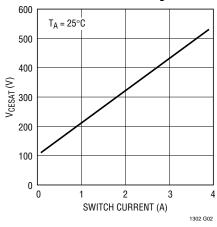

### TYPICAL PERFORMANCE CHARACTERISTICS

#### **No-Load Quiescent Current Circuit of Figure 1**

#### **Switch Saturation Voltage**

#### **Switch Saturation Voltage**

#### LT1302 Feedback Voltage

#### LT1302-5 Sense Pin Resistance

#### **Quiescent Current**

#### **Error Amplifier Offset Voltage**

### LT1302-5 Output Voltage

#### **Maximum On-Time**

### TYPICAL PERFORMANCE CHARACTERISTICS

## PIN FUNCTIONS

**GND (Pin 1):** Signal Ground. Feedback resistor and  $0.1\mu F$  ceramic bypass capacitor from  $V_{IN}$  should be connected directly to this pin.

$V_{C}$  (Pin 2): Frequency Compensation Pin. Connect series RC to GND. Keep trace short.

**SHDN (Pin 3):** Shutdown. Pull high to effect shutdown; tie to ground for normal operation.

**FB/Sense (Pin 4):** Feedback/Sense. On the LT1302 this pin connects to CMP1 input. On the LT1302-5 this pin connects to the output resistor string.

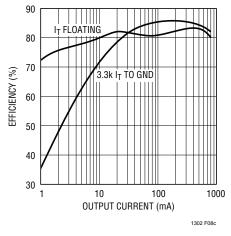

$I_T$  (**Pin 5**): Normally left floating. Addition of a 3.3k resistor to GND forces the LT1302 into current mode at light loads. Efficiency drops at light load but increases at medium loads. See Applications Information section.

$V_{IN}$  (Pin 6): Supply Pin. Must be bypassed with: (1) a 0.1 μF ceramic to GND, and (2) a large value electrolytic to PGND. When  $V_{IN}$  is greater than 5V, a low value resistor (2 $\Omega$  to 10 $\Omega$ ) is recommended to isolate the  $V_{IN}$  pin from input supply noise.

### PIN FUNCTIONS

**SW (Pin 7):** Switch Pin. Connect inductor and diode here. Keep layout short and direct.

**PGND (Pin 8):** Power Ground. Pins 8 and 1 should be connected under the package. In the SO package, pins 1

and 8 are thermally connected to the die. One square inch of PCB copper provides an adequate heat sink for the device.

### **BLOCK DIAGRAMS**

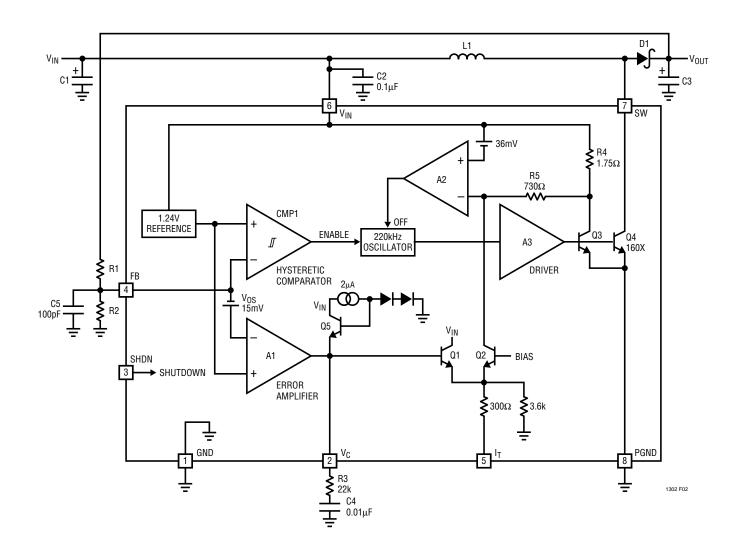

Figure 2. LT1302 Block Diagram

### **BLOCK DIAGRAMS**

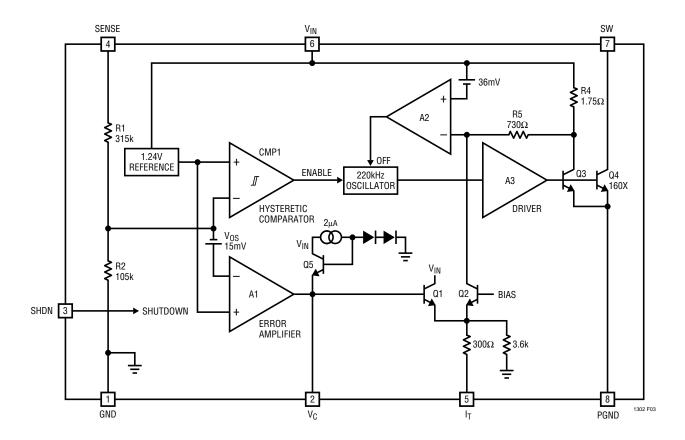

Figure 3. LT1302-5 Block Diagram

### **OPERATION**

The LT1302's operation can best be understood by examining the block diagram in Figure 2. The LT1302 operates in one of two modes, depending on load. With light loads, comparator CMP1 controls the output; with heavy loads, control is passed to error amplifier A1. Burst Mode operation consists of monitoring the FB pin voltage with hysteretic comparator CMP1. When the FB voltage, related to the output voltage by external attenuator R1 and R2, falls below the 1.24V reference voltage, the oscillator is enabled. Switch Q4 alternately turns on, causing current buildup in inductor L1, then turns off, allowing the built-up current to flow into output capacitor C3 via D1. As the output voltage increases, so does the FB voltage; when it exceeds the reference plus

CMP1's hysteresis (about 5mV) CMP1 turns the oscillator off. In this mode, peak switch current is limited to approximately 1A by A2, Q2, and Q3. Q2's current, set at  $34\mu\text{A}$ , flows through R5, causing A2's negative input to be 25mV lower than  $V_{IN}$ . This node must fall more than 36mV below  $V_{IN}$  for A2 to trip and turn off the oscillator. The remaining 11mV is generated by Q3's current flowing through R4. Emitter-area scaling sets Q3's collector current to 0.625% of switch Q4's current. When Q4's current is 1A, Q3's current is 6.25mA, creating an 11mV drop across R4 which, added to R5's 25mV drop, is enough to trip A2.

When the output load is increased to the point where the 1A peak current cannot support the output voltage,

### **OPERATION**

CMP1 stays on and the peak switch current is regulated by the voltage on the  $V_{C}$  pin (A1's output).  $V_{C}$  drives the base of Q1. As the  $V_{C}$  voltage rises, Q2 conducts less current, resulting in less drop across R5. Q4's peak current must then increase in order for A2 to trip. This current mode control results in good stability and immunity to input voltage variations. Because this is a linear,

closed-loop system, frequency compensation is required. A series RC from  $V_{\text{C}}$  to ground provides the necessary pole-zero combination.

The LT1302-5 incorporates feedback resistors R1 and R2 into the device. Output voltage is set at 5.05V in Burst Mode, dropping to 4.97V in current mode.

## APPLICATIONS INFORMATION

#### **Inductor Selection**

Inductors used with the LT1302 must fulfill two requirements. First, the inductor must be able to handle current of 2.5A to 3A without runaway saturation. Rod or drum core units usually saturate gradually and it is acceptable to exceed manufacturers' published saturation currents by 20% or so. Second, it should have low DCR, under  $0.05\Omega$ so that copper loss is kept low. Inductance value is not critical. Generally, for low voltage inputs down to 2V, a 10µH inductor is recommended (such as Coilcraft DO3316-103). For inputs above 4V to 5V use a 22µH unit (such as Coilcraft D03316-223). Switching frequency can reach up to 400kHz so the core material should be able to handle high frequency without loss. Ferrite or molypermalloy cores are a better choice than powdered iron. If EMI is a concern a toroidal inductor is suggested, such as Coiltronics CTX20-4.

For a boost converter, duty cycle can be calculated by the following formula:

$$DC = 1 - \left(\frac{V_{IN}}{V_{OUT}}\right)$$

A special situation exists where the  $V_{OUT}/V_{IN}$  differential is high, such as a 2V-to-12V converter. The required duty cycle is higher than the LT1302 can provide, so the converter must be designed for *discontinuous* operation. This means that inductor current goes to zero during the switch off-time. In the 2V-to-12V case, inductance must be low enough so that current in the inductor can reach 2A in a single cycle. Inductor value can be defined by:

$$L \le \frac{\left(V_{IN} - V_{SW}\right) \times t_{ON}}{2A}$$

With the 2V input a value of  $3.3\mu H$  is acceptable. Since the inductance is so low, usually a smaller core size can be used. Efficiency will not be as high as for the continuous case since peak currents will necessarily be higher.

Table 1 lists inductor suppliers along with appropriate part numbers.

Table 1. Recommended Inductors

| VENDOR      | PART NO.      | VALUE(µH) | PHONE NO.      |

|-------------|---------------|-----------|----------------|

| Coilcraft   | D03316-103    | 10        | (708) 639-6400 |

|             | D03316-153    | 15        | , ,            |

|             | D03316-223    | 22        |                |

| Coiltronics | CTX10-2       | 10        | (407) 241-7876 |

|             | CTX20-4       | 20        |                |

| Dale        | LPT4545-100LA | 10        | (605) 665-9301 |

|             | LPT4545-200LA | 20        |                |

| Sumida      | CD105-100     | 10        | (708) 956-0666 |

|             | CD105-150     | 15        |                |

|             | CDR125-220    | 22        |                |

### **Capacitor Selection**

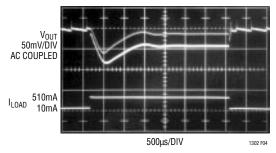

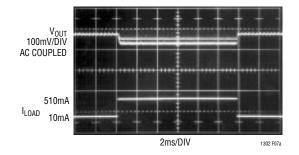

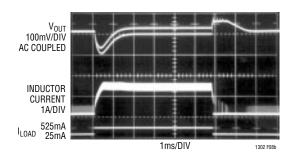

The output capacitor should have low ESR for proper performance. A high ESR capacitor can result in "mode-hopping" between current mode and Burst Mode at high load currents because the output voltage will increase by  $I_{SW} \times ESR$  when the inductor current is flowing into the diode. Figure 4 shows output voltage of an LT1302-5 boost converter with two 220µF AVX TPS capacitors at the output. Ripple voltage at a 510mA load is about  $30\text{mV}_{P-P}$

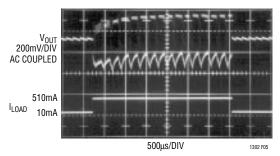

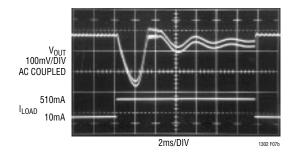

and there is no low frequency component. The total ESR is under  $0.03\Omega$ . If a single  $100\mu\text{F}$  aluminum electrolytic capacitor is used instead, the converter mode-hops between current mode and Burst Mode due to high ESR, causing the voltage comparator to trip as shown in Figure 5. The ripple voltage is now over  $500\text{mV}_{\text{P-P}}$  and contains a low frequency component. Maximum allowable output capacitor ESR can be calculated by the following formula:

$$ESR_{MAX} = \frac{V_{OS} \times V_{OUT}}{V_{RFF} \times 1A}$$

where,

$$V_{OS} = 15 \text{mV}$$

$$V_{REF} = 1.24V$$

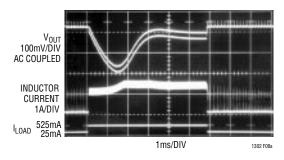

Figure 4. Low ESR Output Capacitor Results in Stable Operation. Ripple Voltage is Under 30mV<sub>P-P</sub>

Figure 5. Inexpensive Electrolytic Capacitor Has High ESR, Resulting in Mode-Hop, Ripple Voltage Amplitude Is Over 500mV<sub>P-P</sub> and Includes Low Frequency Component

#### **Input Capacitor**

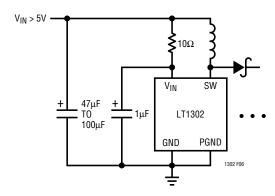

The input supply should be decoupled with a good quality electrolytic capacitor close to the LT1302 to provide a stable input supply. Long leads or traces from power source to the switcher can have considerable impedance at the LT1302's switching frequency. The input capacitor provides a low impedance at high frequency. A 0.1  $\mu$ C ceramic capacitor is required right at the  $V_{IN}$  pin. When the input voltage can be above 5V, a  $10\Omega/1\mu$ C decoupling network for  $V_{IN}$  is recommended as detailed in Figure 6. This network is also recommended when driving a transformer.

Figure 6. A  $10\Omega/1\mu F$  Decoupling Network at  $V_{IN}$  Is Recommended When Input Voltage Is Above 5V

Table 2 lists capacitor vendors along with device types.

**Table 2. Recommended Capacitors**

| VENDOR  | SERIES | TYPE          | PHONE NO.      |

|---------|--------|---------------|----------------|

| AVX     | TPS    | Surface Mount | (803) 448-9411 |

| Sanyo   | OS-CON | Through Hole  | (619) 661-6835 |

| Sprague | 595D   | Surface Mount | (603) 224-1961 |

#### **Diode Selection**

A 2A Schottky diode such as Motorola MBRS130LT3 has been found to be the best available. Other choices include 1N5821 or MBRS130T3. Do not use "general purpose" diodes such as 1N4001. They are much too slow for use in switching regulator applications.

INTERPLEMENT TECHNOLOGY

#### **Frequency Compensation**

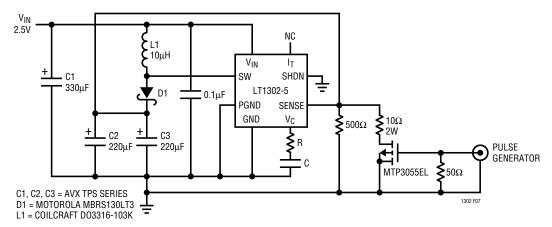

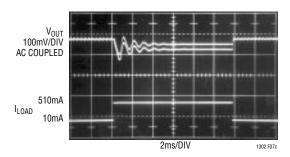

Obtaining proper RC values for the frequency compensation network is largely an empirical procedure, since variations in input and output voltage, topology, capacitor ESR and inductance make a simple formula elusive. As an example, consider the case of a 2.5V to 5V boost converter supplying 500mA. To determine optimum compensation, the circuit is built and a transient load is applied to the circuit. Figure 7 shows the setup.

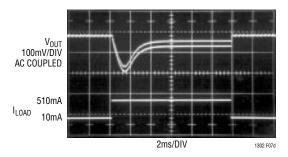

In Figure 7a, the  $V_{C}$  pin is simply left floating. Although output voltage is maintained and transient response is good, switch current rises instantaneously to the internal current limit upon application of load. This is an undesirable situation as it places maximum stress on the switch and the other power components. Additionally, efficiency is well down from its optimal value. Next, a  $0.1\mu F$  capacitor is connected with no resistor. Figure 7b details response. Although the circuit eventually stabilizes, the loop is quite underdamped. Initial output "sag" exceeds 5%. Aberrant

behavior in the 4th graticule is the result of the LT1302's Burst Mode comparator turning off all switching as output voltage rises above its threshold.

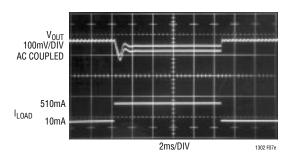

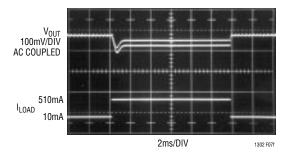

In Figure 7c, the  $0.1\mu F$  capacitor has been replaced by a  $0.01\mu F$  unit. Undershoot is less but the response is still underdamped. Figure 7d shows the results of the  $0.1\mu F$  capacitor and a 10k resistor in series. Now some amount of damping is observed, and behavior is more controlled. Figure 7e details response with a  $0.01\mu F/10k$  series network. Undershoot is down to around 100mV, or 2%. A slight underdamping is still noticeable.

Finally, a  $0.01\mu F/24k$  series network results in the response shown in Figure 7f. This has optimal damping, undershoot less than 100mV and settles in less than 1ms.

The  $V_C$  pin is sensitive to high frequency noise. Some layouts may inject enough noise to modulate peak switch current at 1/2 the switching frequency. A small capacitor connected from  $V_C$  to ground will eliminate this. Do not exceed 1/10 of the compensation capacitor value.

Figure 7. Boost Converter with Simulated Load

Figure 7a. V<sub>C</sub> Pin Left Unconnected. Output Shows Low Frequency Components Under Load

Figure 7b. 0.1  $\mu F$  from  $V_C$  to Ground. Better, but More Improvement Needed

Figure 7c. 0.01µF from V<sub>C</sub> to Ground. Underdamped Response Requires Series R

Figure 7d. 0.1µF with 10k Series RC. Classic Overdamped Response

Figure 7e.  $0.01\mu F$ , 10k Series RC Shows Good Transient Response. Slight Underdamping Still Noticeable

Figure 7f. 0.01 $\mu$ F, 24k Series RC Results in Optimum Response

#### I<sub>T</sub> Pin

The  $I_T$  pin is used to disable Burst Mode, forcing the LT1302 to operate in current mode even at light load. To disable Burst Mode, 3.3k resistor R1 is connected from  $I_T$  to gound. More conservative frequency compensation must be used when in this mode. A  $0.1\mu F$  capacitor and 4.7k resistor from  $V_C$  to ground has been found to be adequate. Low frequency Burst Mode ripple can be reduced or eliminated using this technique in many applications.

To illustrate, the transient load response of Figure 8's circuit is pictured without and with R1. Figure 8a shows output voltage and inductor current without the resistor. Note the 6kHz burst rate when the converter is delivering 25mA. By adding the 3.3k resistor, the low frequency bursting is eliminated, as shown in Figure 8b. This feature is useful in systems that contain audio circuitry. At very light or zero load, switching frequency drops and eventu-

Figure 8. Addition of R1 Eliminates Low Frequency Output Ripple in This 2.5V to 5V Boost Converter

Figure 8a. I<sub>T</sub> Pin Floating. Note 6kHz Burst Rate at  $I_{LOAD}$  = 25mA. 0.1 $\mu$ F/4.7k Compensation Network Causes 220mV Undershoot

ally reaches audio frequencies, but at a much lighter load than without the  $I_T$  feature. At some input voltage/load current combinations, some residual bursting may occur at frequencies out of the audio band.

Figure 8b. 3.3k Resistor from  $I_T$  Pin to Ground Forces LT1302 into Current Mode Regardless of Load. Audio Frequency Component Eliminated

Figure 8c. 3.3k Resistor for  $I_T$  to Ground Increases Efficiency at Moderate Load, Decreases at Light Load

The  $I_T$  pin cannot be used as a soft-start. Large capacitors connected to the pin will cause erratic operation. If operating the device in Burst Mode, let the pin float. Keep high dV/dt signals away from the pin.

Figure 8c details efficiency with and without the addition of R1. Burst Mode operation keeps efficiency high at light load with  $I_T$  floating. Efficiency falls off at light load with R1 added because the LT1302 cannot transition into Burst Mode.

#### Layout

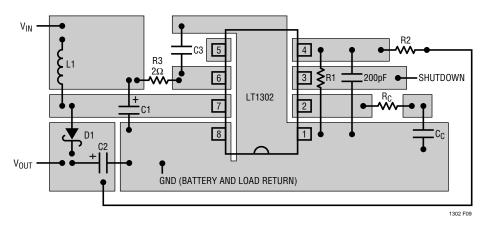

The high speed, high current switching associated with the LT1302 mandates careful attention to layout. Follow the suggested component placement in Figure 9 for proper operation. High current functions are separated by the package from sensitive control functions. Feedback resistors R1 and R2 should be close to the feedback pin (pin4). Noise can easily be coupled into this pin if care is not taken. A small capacitor (100pF to 200pF) from FB to ground provides a high frequency bypass. If the LT1302 is operated off a three-cell or higher input, R3 ( $2\Omega$  to  $10\Omega$ ) in series with V<sub>IN</sub> is recommended. This isolates the device from noise spikes on the input supply. Do not put in R3 if the device must operate from a 2V input, as input current will cause the voltage at the LT1302's V<sub>IN</sub> pin to go below 2V. The 0.1µF ceramic bypass capacitor C3 (use X7R, not Z5U) should be mounted as close as possible to the package. When R3 is used. C3 should be a 1uF tantalum unit. Grounding should be segregated as illustrated. C3's ground trace should not carry switch current. Run a

Figure 9. Suggested Component Placement for LT1302

separate ground trace up under the package as shown. The battery and load return should go to the power side of the ground copper.

#### **Thermal Considerations**

The LT1302 contains a thermal shutdown feature which protects against excessive internal (junction) temperature. If the junction temperature of the device exceeds the protection threshold, the device will begin cycling between normal operation and an off state. The cycling is not harmful to the part. The thermal cycling occurs at a slow rate, typically 10ms to several seconds, which depends on the power dissipation and the thermal time constants of the package and heat sinking. Raising the ambient temperature until the device begins thermal shutdown gives a good indication of how much margin there is in the thermal design.

For surface mount devices heat sinking is accomplished by using the heat spreading capabilities of the PC board and its copper traces. Experiments have shown that the heat spreading copper layer does not need to be electrically connected to the tab of the device. The PCB material can be very effective at transmitting heat between the pad area attached to pins 1 and 8 of the device, and a ground or power plane layer either inside or on the opposite side of the board. Although the actual thermal resistance of the PCB material is high, the length/area ratio of the thermal resistance between the layer is small. Copper board stiffeners and plated through holes can also be used to spread the heat generated by the device.

Table 3 lists thermal resistance for the SO package. Measured values of thermal resistance for several different board sizes and copper areas are listed for each surface mount package. All measurements were taken in still air on 3/32" FR-4 board with 1oz copper. This data can be used as a rough guideline in estimating thermal resistance. The thermal resistance for each application will be affected by thermal interactions with other components as well as board size and shape.

Table 3. S8 Package, 8-Lead Plastic SO

| COPPER AREA |             |             | THERMAL RESISTANCE    |

|-------------|-------------|-------------|-----------------------|

| TOPSIDE*    | BACKSIDE    | BOARD AREA  | (JUNCTION-TO-AMBIENT) |

| 2500 sq. mm | 2500 sq. mm | 2500 sq. mm | 60°C/W                |

| 1000 sq. mm | 2500 sq. mm | 2500 sq. mm | 62°C/W                |

| 225 sq. mm  | 2500 sq. mm | 2500 sq. mm | 65°C/W                |

| 100 sq. mm  | 2500 sq. mm | 2500 sq. mm | 69°C/W                |

| 100 sq. mm  | 1000 sq. mm | 2500 sq. mm | 73°C/W                |

| 100 sq. mm  | 225 sq. mm  | 2500 sq. mm | 80°C/W                |

| 100 sq. mm  | 100 sq. mm  | 2500 sq. mm | 83°C/W                |

<sup>\*</sup> Pins 1 and 8 attached to topside copper

N8 Package, 8-Lead DIP:

Thermal Resistance (Junction-to-Ambient) = 100°C/W

### **Calculating Temperature Rise**

Power dissipation internal to the LT1302 in a boost regulator configuration is approximately equal to:

$$P_{D} = I_{OUT}^{2} R \left[ \left( \frac{V_{OUT} + V_{D}}{V_{IN}} \right)^{2} - \left( \frac{V_{OUT} + V_{D}}{V_{IN}} \right)^{2} - \left( \frac{V_{OUT} + V_{D}}{V_{IN}} \right) \right]$$

$$+\frac{I_{OUT}\Big(V_{OUT}+V_D-V_{IN}\Big)}{27}$$

The first term in this equation is due to switch "on-resistance." The second term is from the switch driver. R is switch resistance, typically  $0.15\Omega$ .  $V_D$  is the diode forward drop.

The temperature rise can be calculated from:

$$\Delta T = P_D \times \theta_{JA}$$

where:

$\Delta T$  = Temperature Rise

P<sub>D</sub> = Device Power Dissipation

$\theta_{JA}$  = Thermal Resistance (Junction-to-Ambient)

As an example, consider a boost converter with the following specifications:

$$V_{IN} = 3V$$

$$V_{OUT} = 6V$$

$$I_{OUT} = 700 \text{mA}$$

Total power loss in the LT1302, assuming R =  $0.15\Omega$  and  $V_D = 0.45V$ , is:

$$P_{D} = \left(700 \text{mA}\right)^{2} \left(0.15 \Omega\right) \left[ \left(\frac{6 + 0.45}{3 - \frac{0.7 \times 6 \times 0.15}{3}}\right)^{2} - \left(\frac{6 + 0.45}{3 - \frac{0.7 \times 6 \times 0.15}{3}}\right) \right] + \frac{\left(0.7\right) \left(6 + 0.45 - 3\right)}{27} \right]$$

$$= 223 \text{mW} + 89 \text{mW} = 312 \text{mW}$$

Using the CS8 package with 100 sq. mm topside and backside heat sinking:

$$\Delta T = (312 \text{mW})(84 ^{\circ} \text{C/W}) = 25.9 ^{\circ} \text{C rise}$$

With the N8 package:

$$\Delta T = 31.2^{\circ}C$$

At a 70°C ambient, die temperature would be 101.2°C.

## TYPICAL APPLICATIONS

#### Single Cell to 5V/150mA Converter

#### 2V to 12V/120mA Converter

### TYPICAL APPLICATIONS

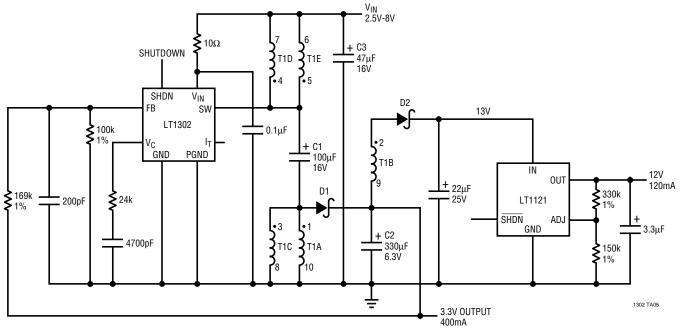

3 Cell to 3.3V Buck-Boost Converter with Auxiliary 12V Regulated Output

- T1 = DALE LPE-6562-A069, 1:3:1:1:1 TURNS RATIO,  $10\mu H$  PRIMARY. DALE (605) 665-9301 D1, D2 = MOTOROLA MBRS130LT3

- - C1 = AVX TPSE107016R0100

- C2 = AVX TPSE337006R0100

- C3 = AVX TPSD476016R0150

#### 2 Li-Ion Cell to 5.8V/600mA DC/DC Converter

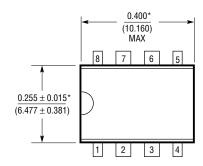

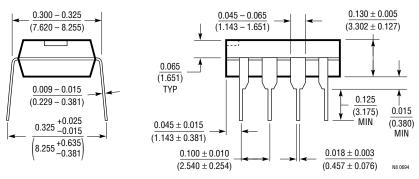

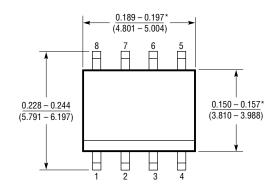

# PACKAGE DESCRIPTION Dimensions in inches (millimeters) unless otherwise noted.

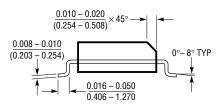

#### N8 Package 8-Lead Plastic DIP

<sup>\*</sup>THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTURSIONS SHALL NOT EXCEED 0.010 INCH (0.254mm).

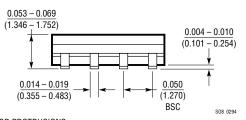

#### S8 Package 8-Lead Plastic SOIC

\*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.006 INCH (0.15mm).

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

### **Analog Devices Inc.:**

<u>LT1302CS8#PBF</u> <u>LT1302CS8-5</u> <u>LT1302CS8+TR</u> <u>LT1302CS8-5#PBF</u> <u>LT1302CN8+PBF</u> <u>LT1302CN8-5#TR</u> LT1302CN8-5#PBF LT1302CN8-5 LT1302CS8+TRPBF LT1302CS8 LT1302CS8