# LTC7883

Quad Output PolyPhase Step-Down DC/DC Voltage Mode Controller with Digital Power System Management

### FEATURES

- PMBus/I<sup>2</sup>C Compliant Serial Interface

- Monitor Voltage, Current, Temperature and Faults

- Program Voltage, Soft-Start/Stop, Sequencing, Margining, AVP and UV/OV/OC Limits

- = 3V  $\leq$  VINSNS  $\leq$  38V, 0.1V (Limited by DrMOS t<sub>ON MIN</sub>)  $\leq$  V<sub>OUT</sub>  $\leq$  5.25V

- ±0.5% Output Voltage Error

- Programmable PWM Frequency or External Clock Synchronization from 250kHz to 2.5MHz

- Accurate PolyPhase<sup>®</sup> Current Sharing

- Internal EEPROM with Fault Logging and ECC

- IC Supply Range: 3V to 13.2V

- Resistor or Inductor DCR Current Sensing

- Power Good Output Voltage Monitor

- Supports Start-Up Into a Prebiased Load

- Optional Resistor Programming for Key Parameters

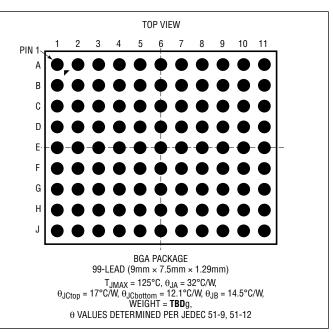

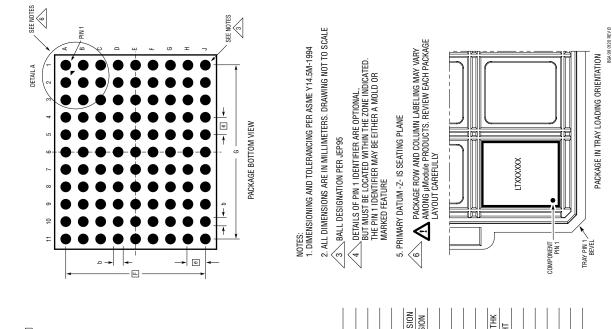

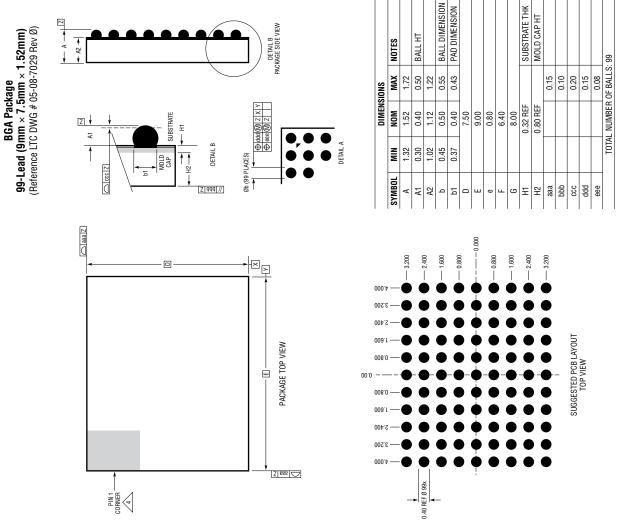

- 99-Lead BGA Package (9mm × 7.5mm)

### **APPLICATIONS**

- High Current Distributed Power Systems

- Servers, Network and Storage Equipment

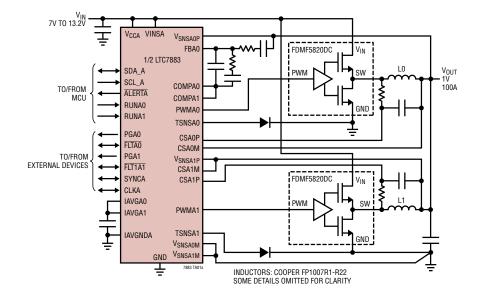

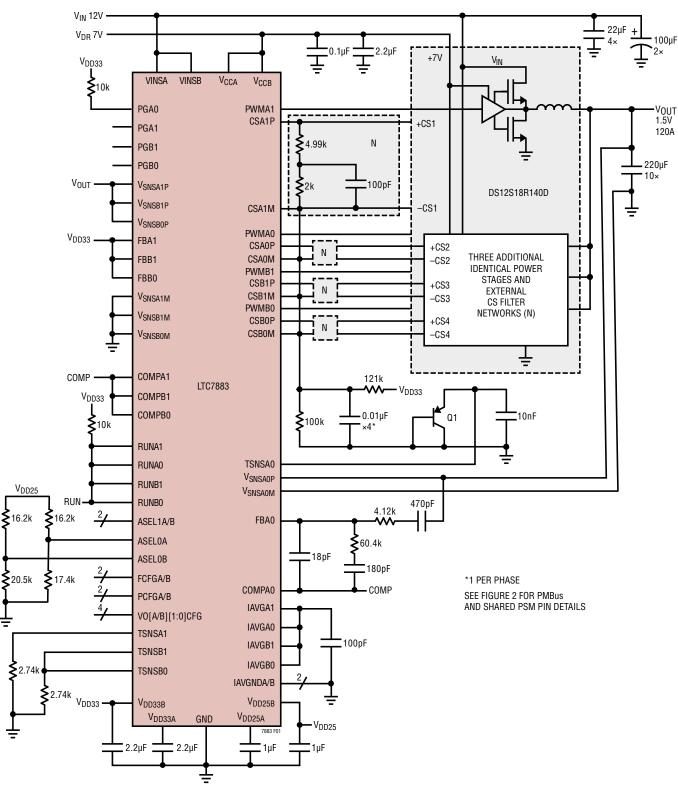

**TYPICAL APPLICATION**

Intelligent Energy Efficient Power Regulation

# DESCRIPTION

The LTC®7883 is a quad, PolyPhase DC/DC synchronous step-down switching regulator controller with PMBus compliant serial interface. It uses a constant frequency, leading-edge modulation, voltage mode architecture for excellent transient response and output regulation. Each PWM channel can produce output voltages from 0.1V to 5.25V using a wide range of 3.3V compatible power stages, including power blocks, DrMOS or discrete FET drivers. LTC7883 devices can operate in parallel, supporting ideal phasor positioning for PolyPhase rails up to 8-phases.

System configuration and monitoring is supported by the LTpowerPlay<sup>®</sup> software tool. The LTC7883 serial interfaces can read back input voltage, output voltage and current, temperature and fault status. Most operating parameters can be set via the digital interfaces or stored in internal EEPROM for use at power-up. Switching frequency and phase, output voltage and device address can also be set using external configuration resistors.

All registered trademarks and trademarks are the property of their respective owners. Protected by U.S. patents, including 5396245, 5859606, 6144194, 6937178, 7420359 and 7000125.

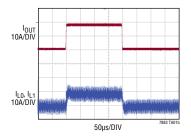

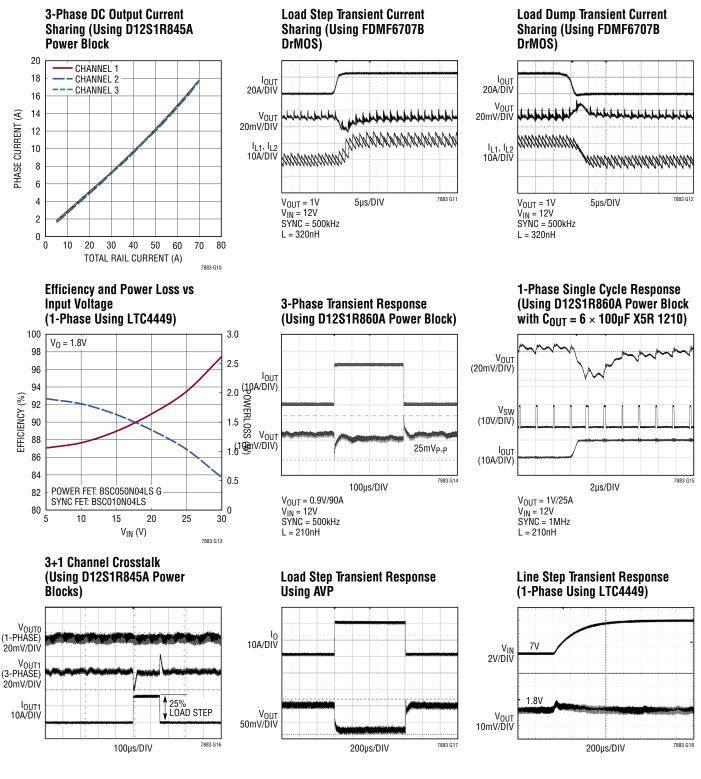

#### Load Step Transient Current Sharing (Using FDMF5820DC DrMOS)

# **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC[A/B]</sub> Supply0.3V to 15V<br>VINS[A/B]0.3V to 40V<br>V <sub>SNS[A/B][1:0]</sub> M0.3V to 40V<br>V <sub>SNS[A/B][1:0]</sub> P, CS[A/B][1:0]P/M0.3V to 4V<br>V <sub>SNS[A/B][1:0]</sub> P, CS[A/B][1:0], -0.3V to 6V<br>FB[A/B][1:0], COMP[A/B][1:0],<br>TSNS[A/B][1:0], IAVGND[A/B], |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IAVG[A/B][1:0]                                                                                                                                                                                                                                                                                   |

| SYNC[A/B], FLT[A/B][1:0], WP[A/B],                                                                                                                                                                                                                                                               |

| PG[A/B][1:0], SHCLK[A/B]0.3V to 3.6V                                                                                                                                                                                                                                                             |

| SCL[A/B], $SDA[A/B]$ , $RUN[A/B][1:0]$ ,                                                                                                                                                                                                                                                         |

| ALERT[A/B]–0.3V to 5.5V<br>ASEL0[A/B], ASEL1[A/B],                                                                                                                                                                                                                                               |

| VO[A/B][1:0]CFG, FCFG[A/B],                                                                                                                                                                                                                                                                      |

| PCFG[A/B] –0.3V to 2.75V                                                                                                                                                                                                                                                                         |

| PWM[A/B][1:0], V <sub>DD25[A/B]</sub>                                                                                                                                                                                                                                                            |

| $V_{DD33[A/B]}$                                                                                                                                                                                                                                                                                  |

| Operating Junction Temperature                                                                                                                                                                                                                                                                   |

| (Notes 2, 3)–40°C to 125°C*<br>Storage Temperature Range–65°C to 150°C*<br>Absolute Maximum Junction Temperature 125°C                                                                                                                                                                           |

\*See Derating EEPROM Retention at Temperature in the Applications Information section for junction temperatures in excess of 125°C.

### PIN CONFIGURATION

# ORDER INFORMATION

|               |                    | PART MARKING* |             | PACKAGE | MSL    | OPERATING JUNCTION |

|---------------|--------------------|---------------|-------------|---------|--------|--------------------|

| PART NUMBER   | PAD OR BALL FINISH | DEVICE        | FINISH CODE | TYPE    | RATING | TEMPERATURE RANGE  |

| LTC7883AY#PBF | SAC305 (RoHS)      | LTC7883Y      | e1          | BGA     | 3      | -40°C to 125°C     |

• Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

• Pad or ball finish code is per IPC/JEDEC J-STD-609.

Recommended LGA and BGA PCB Assembly and Manufacturing Procedures

• LGA and BGA Package and Tray Drawings

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_J = 25^{\circ}C$  (Note 2). Specifications apply to both units with  $V_{CC} = 5V$ ,  $V_{SNSP} = 1.8V$ ,  $V_{SNSM} = IAVGND = GND = 0V$ ,  $f_{SYNC} = 500$ kHz (externally driven) unless otherwise specified.

| SYMBOL                   | PARAMETER                                                                                            | CONDITIONS                                                                                                   |   | MIN      | ТҮР            | MAX      | UNITS        |

|--------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---|----------|----------------|----------|--------------|

| IC Supply                | I                                                                                                    | 1                                                                                                            |   |          |                |          |              |

| V <sub>CC</sub>          | V <sub>CC</sub> Voltage Range                                                                        | V <sub>DD33</sub> = Internal LDO                                                                             |   | 4.5      |                | 13.8     | V            |

| V <sub>DD33_EXT</sub>    | V <sub>DD33</sub> Voltage Range                                                                      | $V_{CC} = V_{DD33}$ (Note 6)                                                                                 | • | 3        |                | 3.6      | V            |

| V <sub>UVLO</sub>        | Undervoltage Lockout Threshold                                                                       | V <sub>DD33</sub> Rising<br>Hysteresis                                                                       | • |          | 42             | 3        | V<br>mV      |

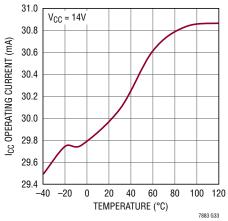

| IQ                       | IC Operating Current                                                                                 | per Unit                                                                                                     |   |          | 32             |          | mA           |

| t <sub>INIT</sub>        | Controller Initialization Time                                                                       | Delay from RESTORE_USER_ALL, MFR_RESET or V <sub>DD33</sub><br>> V <sub>UVLO</sub> Until TON_DELAY Can Begin |   |          | 35             |          | ms           |

| V <sub>DD33</sub> Linear | Regulators                                                                                           |                                                                                                              |   |          |                |          |              |

| V <sub>DD33</sub>        | V <sub>DD33</sub> Regulator Output Voltage                                                           | $V_{CC} \ge 4.5V$                                                                                            |   | 3.2      | 3.3            | 3.4      | V            |

| I <sub>DD33</sub>        | V <sub>DD33</sub> Current Limit                                                                      | V <sub>DD33</sub> = 2.8V<br>V <sub>DD33</sub> = 0V                                                           |   |          | 85<br>40       |          | mA<br>mA     |

| V <sub>DD25</sub> Linear | Regulators                                                                                           |                                                                                                              |   |          |                |          | <u> </u>     |

| V <sub>DD25</sub>        | V <sub>DD25</sub> Regulator Output Voltage                                                           |                                                                                                              |   | 2.25     | 2.5            | 2.75     | V            |

| I <sub>DD25</sub>        | V <sub>DD25</sub> Current Limit                                                                      |                                                                                                              |   |          | 95             |          | mA           |

| PWM Control              | Loops                                                                                                |                                                                                                              |   |          |                |          |              |

| VINS                     | V <sub>IN</sub> Sense Voltage Range                                                                  |                                                                                                              |   | 3        |                | 38       | V            |

| R <sub>VINS</sub>        | VINS Input Resistance                                                                                |                                                                                                              |   |          | 278            |          | kΩ           |

| V <sub>OUT_R0</sub>      | Range 0 Maximum V <sub>OUT</sub><br>Range 0 Set Point Error (Note 7)<br>Range 0 Set Point Resolution | $0.6V \le V_{OUT} \le 5V$                                                                                    | • | -0.5     | 5.25<br>1.375  | 0.5      | V<br>%<br>mV |

| V <sub>OUT_R1</sub>      | Range 1 Maximum V <sub>OUT</sub><br>Range 1 Set Point Error (Note 7)<br>Range 1 Set Point Resolution | $0.6V \le V_{OUT} \le 2.5V$                                                                                  | • | -0.5     | 2.65<br>0.6875 | 0.5      | V<br>%<br>mV |

| I <sub>VSNS</sub>        | V <sub>SNS</sub> Input Current                                                                       | $V_{SNSP} = 5.5V$<br>$V_{SNSM} = 0V$                                                                         |   |          | 235<br>335     |          | μA<br>μA     |

| V <sub>LINEREG</sub>     | V <sub>CC</sub> Line Regulation, No Output Servo                                                     | $4.5V \le V_{CC} \le 13.2V$ (See Test Circuit)                                                               |   | -0.02    |                | 0.02     | %/V          |

| AVP                      | AVP $\Delta V_{OUT}$                                                                                 | AVP = 10%, VOUT_COMMAND = 1.8V,<br>CS Differential Step 3mV to 12mV<br>with IOUT_OC_WARN_LIMIT = 15mV        |   | -118     | -108           | -96      | mV           |

| A <sub>V(OL)</sub>       | Error Amplifier Open-Loop Voltage Gain                                                               |                                                                                                              |   |          | 87             |          | dB           |

| SR                       | Error Amplifier Slew Rate                                                                            |                                                                                                              |   |          | 9.5            |          | V/µs         |

| f <sub>0dB</sub>         | Error Amplifier Bandwidth                                                                            | (Note 12)                                                                                                    |   |          | 30             |          | MHz          |

| ICOMP                    | Error Amplifier Output Current                                                                       | Sourcing<br>Sinking                                                                                          |   |          | -2.6<br>34     |          | mA<br>mA     |

| R <sub>VSFB</sub>        | Resistance Between V <sub>SNSP</sub> and FB                                                          | Range O<br>Range 1                                                                                           | • | 52<br>37 | 67<br>49       | 83<br>61 | kΩ<br>kΩ     |

| VISENSE                  | CS Differential Input Range                                                                          |                                                                                                              |   |          | ±70            |          | mV           |

| IISENSE                  | CSP/M Input Current                                                                                  | $0V \le V_{PIN} \le 5.5V$                                                                                    |   | -1       | ±0.1           | 1        | μA           |

| I <sub>AVG_VOS</sub>     | IAVG Current Sense Offset                                                                            | Referred to CS Inputs                                                                                        |   | -600     | ±175           | 650      | μV<br>μV     |

| V <sub>SIOS</sub>        | Slave Current Sharing Offset                                                                         | Referred to CS Inputs                                                                                        |   | -800     | ±300           | 700      | μV<br>μV     |

| f <sub>SYNC</sub>        | SYNC Frequency Error                                                                                 | 250kHz ≤ f <sub>SYNC</sub> ≤ 1.25MHz                                                                         |   | -10      |                | 10       | %            |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at TJ = 25°C (Note 2). Specifications apply to both units with  $V_{CC} = 5V$ ,  $V_{SNSP} = 1.8V$ ,  $V_{SNSM} = IAVGND = GND = 0V$ ,  $f_{SYNC} = 500$ kHz (externally driven) unless otherwise specified.

| SYMBOL                | PARAMETER                                                                                                  | CONDITIONS                                                                                                                                                                                                                                                                                                |   | MIN                  | ТҮР                                  | MAX               | UNITS                  |

|-----------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------|--------------------------------------|-------------------|------------------------|

| Input Voltage S       | Supervisor                                                                                                 |                                                                                                                                                                                                                                                                                                           |   |                      |                                      |                   |                        |

| V <sub>ON_TOL</sub>   | Input ON/OFF Threshold Error                                                                               | $15V \le V_{IN_{ON}} \le 35V$                                                                                                                                                                                                                                                                             | • | -2                   |                                      | 2                 | %                      |

| N <sub>VON</sub>      | Input ON/OFF Threshold Resolution                                                                          |                                                                                                                                                                                                                                                                                                           |   |                      | 143                                  |                   | mV                     |

| Output Voltage        | Supervisors                                                                                                |                                                                                                                                                                                                                                                                                                           |   |                      |                                      |                   |                        |

| V <sub>UVOV_R0</sub>  | Range 0 Maximum Threshold<br>Range 0 Error<br>Range 0 Threshold Resolution<br>Range 0 Threshold Hysteresis | $2V \le V_{OUT} \le 5V$ (Falling for UV and Rising for OV)                                                                                                                                                                                                                                                | • | -1                   | 5.5<br>11<br>50                      | 1                 | V<br>%<br>mV<br>mV     |

| V <sub>UVOV_R1</sub>  | Range 1 Maximum Threshold<br>Range 1 Error<br>Range 1 Threshold Resolution<br>Range 1 Threshold Hysteresis | $1V \le V_{OUT} \le 2.5V$ (Falling for UV and Rising for OV)                                                                                                                                                                                                                                              | • | -1                   | 2.75<br>5.5<br>25                    | 1                 | V<br>%<br>mV<br>mV     |

| <b>Output Current</b> | Supervisors                                                                                                |                                                                                                                                                                                                                                                                                                           |   |                      |                                      |                   |                        |

| V <sub>ILIM_TOL</sub> | Output Current Limit Tolerance<br>CSP – CSM                                                                | $\begin{array}{l} 15mV < CSP - CSM \leq 30mV \\ 30mV < CSP - CSM \leq 50mV \\ 50mV < CSP - CSM \leq 70mV \end{array}$                                                                                                                                                                                     | • | -1.7<br>-2.5<br>-5.2 |                                      | 1.7<br>2.5<br>5.2 | mV<br>mV<br>mV         |

| N <sub>ILIM</sub>     | CSP – CSM Threshold Resolution                                                                             | 1LSB                                                                                                                                                                                                                                                                                                      |   |                      | 0.4                                  |                   | mV                     |

| ADC Readback          | Telemetry (Note 8)                                                                                         |                                                                                                                                                                                                                                                                                                           |   |                      |                                      |                   |                        |

| N <sub>VIN</sub>      | VINS Readback Resolution                                                                                   | (Note 9)                                                                                                                                                                                                                                                                                                  |   |                      | 10                                   |                   | Bits                   |

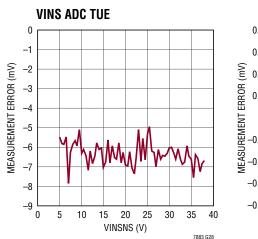

| V <sub>IN_TUE</sub>   | VINS Total Unadjusted Readback Error                                                                       | $4.5V \le VINS \le 38V$                                                                                                                                                                                                                                                                                   | • |                      |                                      | 0.5<br>2          | %                      |

| N <sub>DC</sub>       | PWM Duty Cycle Resolution                                                                                  | (Note 9)                                                                                                                                                                                                                                                                                                  |   |                      | 10                                   |                   | Bits                   |

| DC <sub>TUE</sub>     | PWM Duty Cycle Total Unadjusted<br>Readback Error                                                          | PWM Duty Cycle = 12.5%                                                                                                                                                                                                                                                                                    |   | -2                   |                                      | 2                 | %                      |

| N <sub>VOUT</sub>     | V <sub>OUT</sub> Readback Resolution                                                                       |                                                                                                                                                                                                                                                                                                           |   |                      | 244                                  |                   | μV                     |

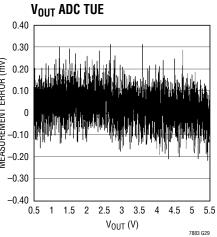

| V <sub>OUT_TUE</sub>  | V <sub>OUT</sub> Total Unadjusted Readback Error                                                           | $0.6V \le V_{OUT} \le 5.5V$ , Constant Load                                                                                                                                                                                                                                                               | • | -0.5                 | ±0.2                                 | 0.5               | %                      |

| N <sub>ISENSE</sub>   | I <sub>OUT</sub> Readback Resolution<br>LSB Step Size (at I <sub>SENSE</sub> <sup>±</sup> )                | $ \begin{array}{l} (\text{Note 9}) \\ 0\text{mV} \leq  \text{CSP} - \text{CSM}  < 16\text{mV} \\ 16\text{mV} \leq  \text{CSP} - \text{CSM}  < 32\text{mV} \\ 32\text{mV} \leq  \text{CSP} - \text{CSM}  < 63.9\text{mV} \\ 63.9\text{mV} \leq  \text{CSP} - \text{CSM}  \leq 70\text{mV} \\ \end{array} $ |   |                      | 10<br>15.625<br>31.25<br>62.5<br>125 |                   | Bits<br>μV<br>μV<br>μV |

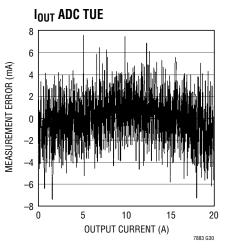

| ISENSE_TUE            | I <sub>OUT</sub> Total Unadjusted Readback Error                                                           | $ \text{CSP} - \text{CSM}  \ge 6\text{mV}, \ 0\text{V} \le \text{V}_{0\text{UT}} \le 5.5\text{V}$                                                                                                                                                                                                         | • |                      | ±1                                   |                   | %                      |

| I <sub>SENSE_OS</sub> | I <sub>OUT</sub> Zero-Code Offset Voltage                                                                  |                                                                                                                                                                                                                                                                                                           |   |                      | ±32                                  |                   | μV                     |

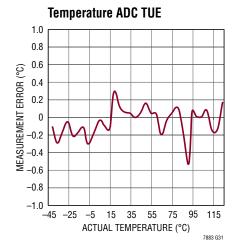

| N <sub>TEMP</sub>     | Temperature Resolution                                                                                     |                                                                                                                                                                                                                                                                                                           |   |                      | 0.25                                 |                   | °C                     |

| T <sub>EXT_TUE</sub>  | External Temperature Total Unadjusted<br>Readback Error                                                    | TSNS ≤ 1.85V (Note 10)<br>MFR_PWM_MODE_LTC3882-1[6] = 0<br>MFR_PWM_MODE_LTC3882-1[6] = 1                                                                                                                                                                                                                  | • | 3<br>7               |                                      | 3<br>7            | 0°<br>0°               |

| T <sub>INT_TUE</sub>  | Internal Temperature Total Unadjusted<br>Readback Error                                                    | Internal Diode (Note 10)                                                                                                                                                                                                                                                                                  |   |                      | ±1                                   |                   | °C                     |

| t <sub>CONVERT</sub>  | Update Rate                                                                                                | (Note 11)                                                                                                                                                                                                                                                                                                 |   |                      | 90                                   |                   | ms                     |

| Internal EEPRO        | IM (Notes 4, 6)                                                                                            |                                                                                                                                                                                                                                                                                                           |   |                      |                                      |                   |                        |

| Endurance             | Number of Write Operations                                                                                 | $0^{\circ}C \le T_{J} \le 85^{\circ}C$ During All Write Operations                                                                                                                                                                                                                                        |   | 10,000               |                                      |                   | Cycles                 |

| Retention             | Stored Data Retention                                                                                      | $T_J \le 125^{\circ}C$                                                                                                                                                                                                                                                                                    |   | 10                   |                                      |                   | Years                  |

| Mass Write Tim        | e STORE_USER_ALL Execution Duration                                                                        | $0^{\circ}C \leq T_J \leq 85^{\circ}C$ During All Write Operations                                                                                                                                                                                                                                        |   |                      | 0.2                                  | 2                 | S                      |

|                       |                                                                                                            |                                                                                                                                                                                                                                                                                                           |   |                      |                                      |                   |                        |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at TJ = 25°C (Note 2). Specifications apply to both units with  $V_{CC} = 5V$ ,  $V_{SNSP} = 1.8V$ ,  $V_{SNSM} = IAVGND = 0V$ ,  $f_{SYNC} = 500$ kHz (externally driven) unless otherwise specified.

| SYMBOL                                  | PARAMETER                                                                                                                                 | CONDITIONS                                                                                               | T | MIN         | TYP     | MAX        | UNITS    |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---|-------------|---------|------------|----------|

| Digital Input                           | s (SCL, SDA, RUN, FLT, SYNC, SHCLK, WP)                                                                                                   |                                                                                                          |   |             |         |            |          |

| V <sub>IH</sub>                         | Input High Voltage                                                                                                                        | SCL, SDA, RUN, FLT<br>SYNC, SHCLK, WP                                                                    | • | 1.35<br>1.8 |         |            | V<br>V   |

| V <sub>IL</sub>                         | Input Low Voltage                                                                                                                         | SCL, SDA, RUN, FLT<br>SYNC, SHCLK, WP                                                                    | • |             |         | 0.8<br>0.6 | V<br>V   |

| V <sub>HYST</sub>                       | Input Hysteresis                                                                                                                          | SCL, SDA                                                                                                 |   |             | 80      |            | mV       |

| I <sub>LKG</sub>                        | Input Pull-Up Current                                                                                                                     | WP = 0V                                                                                                  |   |             | 10      |            | μA       |

| C <sub>IN</sub>                         | Input Capacitance                                                                                                                         | SCL, SDA, RUN, FLT, SYNC, SHCLK (Note 12)                                                                |   |             |         | 10         | pF       |

| t <sub>FILT</sub>                       | Input Digital Filter Delay                                                                                                                | FLT<br>RUN                                                                                               |   |             | 3<br>10 |            | μs<br>μs |

| Digital Outpu                           | its (SCL, SDA, RUN, FLT, SYNC, SHCLK, ALI                                                                                                 | ERT, PWM, PG)                                                                                            |   |             |         |            |          |

| V <sub>OL</sub>                         | Output Low Voltage                                                                                                                        | $I_{SINK}$ = 3mA; SCL, SDA, RUN, FLT, SYNC, SHCLK, ALERT $I_{SINK}$ = 2mA; PWM, PG                       | • |             | 0.2     | 0.4<br>0.3 | V<br>V   |

| V <sub>OH</sub>                         | PWM Output High Voltage                                                                                                                   | I <sub>SOURCE</sub> = 2mA                                                                                |   | 2.7         |         |            | V        |

| I <sub>LKG</sub>                        | Output Leakage Current                                                                                                                    | $OV \leq PWM$ , $PG \leq V_{DD33}$<br>$OV \leq FLT$ , SYNC, SHCLK $\leq 3.6V$<br>$OV \leq RUN \leq 5.5V$ |   | -1<br>-5    |         | 1<br>5     | μΑ<br>μΑ |

|                                         |                                                                                                                                           | $0V \le SCL$ , SDA, $\overline{ALERT} \le 5.5V$                                                          |   | -5          |         | 5          | μA       |

| t <sub>R0</sub>                         | PWM Output Rise Time                                                                                                                      | C <sub>LOAD</sub> = 30pF, 10% to 90%                                                                     |   |             | 5       |            | ns       |

| t <sub>FO</sub>                         | PWM Output Fall Time                                                                                                                      | C <sub>LOAD</sub> = 30pF, 90% to 10%                                                                     |   |             | 4       |            | ns       |

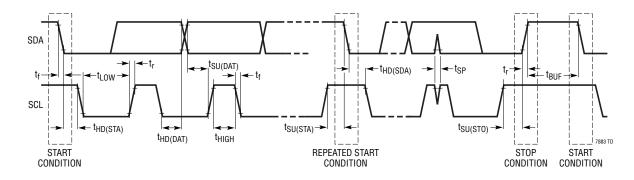

| Serial Bus Ti                           |                                                                                                                                           | 1                                                                                                        |   | 10          |         | 400        |          |

| f <sub>SMB</sub>                        | Serial Bus Operating Frequency                                                                                                            |                                                                                                          |   | 10          |         | 400        | kHz      |

| t <sub>buf</sub><br>t <sub>hd,sta</sub> | Bus Free Time Between Stop and Start<br>Hold Time After (Repeated) Start<br>Condition. After This Period, the First<br>Clock Is Generated |                                                                                                          | • | 1.3<br>0.6  |         |            | µs<br>µs |

| t <sub>SU,STA</sub>                     | Repeated Start Condition Setup Time                                                                                                       |                                                                                                          |   | 0.6         |         |            | μs       |

| t <sub>SU,STO</sub>                     | Stop Condition Setup Time                                                                                                                 |                                                                                                          |   | 0.6         |         |            | μs       |

| t <sub>hd,dat</sub>                     | Data Hold Time:<br>Receiving Data<br>Transmitting Data                                                                                    |                                                                                                          | • | 0<br>0.3    |         | 0.9        | ns<br>µs |

| t <sub>SU,DAT</sub>                     | Input Data Setup Time                                                                                                                     |                                                                                                          |   | 100         |         |            | ns       |

| t <sub>TIMEOUT</sub>                    | Clock Low Timeout                                                                                                                         |                                                                                                          |   | 25          |         | 35         | ms       |

| t <sub>LOW</sub>                        | Serial Clock Low Period                                                                                                                   |                                                                                                          |   | 1.3         |         | 10000      | μs       |

| t <sub>HIGH</sub>                       | Serial Clock High Period                                                                                                                  |                                                                                                          |   | 0.6         |         |            | μs       |

# **ELECTRICAL CHARACTERISTICS**

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC7883 is specified over the -40°C to 125°C operating junction temperature range. High Junction temperatures degrade operating lifetimes; operating lifetime is derated for junction temperatures greater than 125°C. Note the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors.

**Note 3:** This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. The maximum rated junction temperature will be exceeded when this protection is active. Continuous operation above the specified absolute maximum operating junction temperature may impair device reliability or permanently damage the device.

**Note 4:** EEPROM endurance, retention and mass write times are guaranteed by design, characterization and correlation with statistical process controls. Minimum retention applies only for devices cycled less than the minimum endurance specification. EEPROM read commands (e.g. RESTORE\_USER\_ALL) are valid over the entire specified operating junction temperature range.

**Note 5:** All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to GND unless otherwise specified.

**Note 6:** Minimum EEPROM endurance, retention and mass write time specifications apply when writing data with  $3.15V \le V_{DD33} \le 3.45V$ . EEPROM read commands are valid over the entire specified  $V_{DD33}$  operating range.

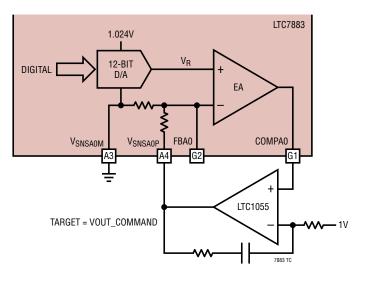

**Note 7:** Specified V<sub>OUT</sub> error with AVP = 0% requires servo mode to be set with MFR\_PWM\_MODE\_LTC3882-1 command bit 6. Performance is guaranteed by testing the LTC7883 in a feedback loop that servos V<sub>OUT</sub> to a specified value.

**Note 8:** ADC tested with PWMs disabled. Comparable capability demonstrated by in-circuit evaluations. Total Unadjusted Error includes all gain and linearity errors, as well as offsets.

**Note 9:** Internal 32-bit calculations using 16-bit ADC results are limited to 10-bit resolution by PMBus Linear 11-bit data format.

**Note 10:** Limits guaranteed by TSNS voltage and current measurements during test, including ADC readback.

**Note 11:** Data conversion is done in round robin fashion. All inputs signals are continuously scanned in sequence resulting in a typical conversion latency of 90ms.

Note 12: Guaranteed by design.

**Note 13:** Do not apply a voltage or current source directly to these pins. They should only be connected to passive RC loads, otherwise permanent damage may occur.

Note 14: Do not apply a voltage source to this pin unless shorted to  $V_{CC}.$  See Electrical Characteristics for applicable limits beyond which permanent damage may occur.

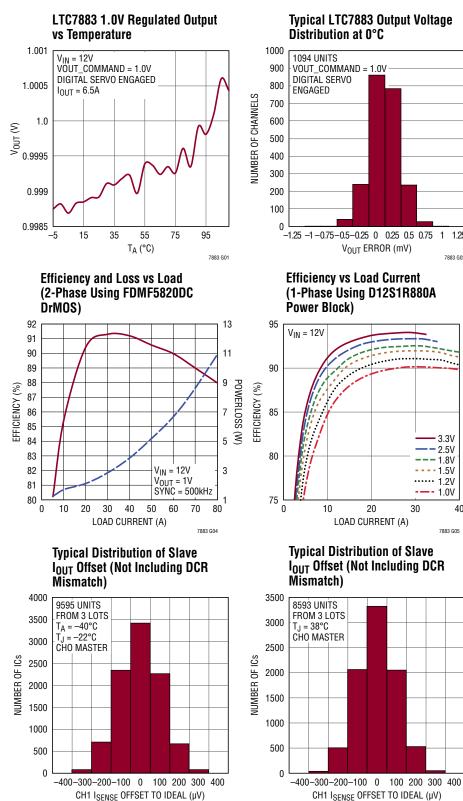

7883 G07

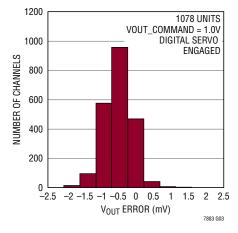

#### Typical LTC78883 Output Voltage Distribution at 105°C

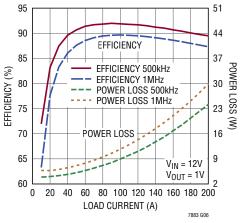

#### Efficiency and Loss vs Load (4-Phase Using LTC7051)

1.25

7883 G02

40

7883 G08

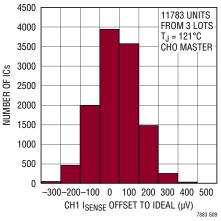

**Typical Distribution of Slave** IOUT Offset (Not Including DCR Mismatch)

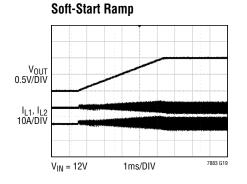

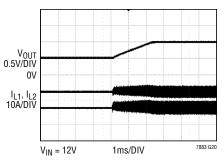

Start-Up Into a Prebiased Load

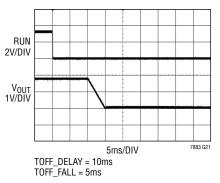

Soft-Off Ramp

**Regulated Output vs Temperature** 1.8000 VOUT\_COMMAND = 1.8V DIGITAL SERVO OFF 1.7995 1.7990 V<sub>0UT</sub> (V) 1.7985 1.7980 1.7975 1.7970 -40 -20 0 20 40 60 80 100 120 TEMPERATURE (°C) 7883 G22

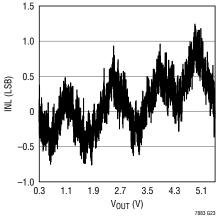

**VOUT\_COMMAND INL**

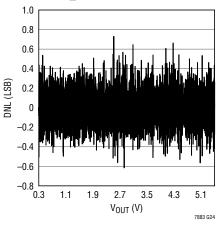

**VOUT\_COMMAND DNL**

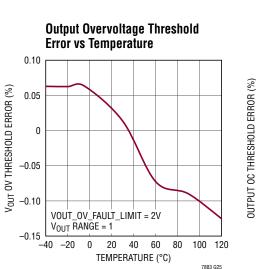

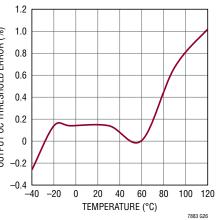

**Output Overcurrent Threshold Error vs Temperature**

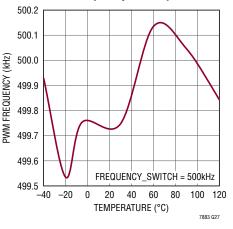

**PWM Frequency vs Temperature**

IC Operating Current vs Temperature

**SHCLK Frequency vs Temperature**

# LTC7883 PIN (BALL) ASSIGNMENTS

|            | PIN N               | · · · · · · · · · · · · · · · · · · · |          |                    | NAME               |

|------------|---------------------|---------------------------------------|----------|--------------------|--------------------|

| BALL       | UNIT A              | UNIT B                                | BALL     | UNIT A             | UNIT B             |

| A1         | V <sub>SNSA1P</sub> |                                       | E6       | GND                | GND                |

| A2         | V <sub>SNSA1M</sub> |                                       | E7       | GND                | GND                |

| A3         | V <sub>SNSA0M</sub> |                                       | E8       | GND                | GND                |

| A4         | V <sub>SNSAOP</sub> |                                       | E9       | GND                | GND                |

| A5         | ALERTA              |                                       | E10      |                    | V <sub>DD25B</sub> |

| A6         | V <sub>CCA</sub>    |                                       | E11      |                    | IAVGND             |

| A7         |                     | ALERTB                                | F1       | COMPA1             |                    |

| A8         |                     | V <sub>SNSB1P</sub>                   | F2       | FBA1               |                    |

| A9         |                     | V <sub>SNSB1M</sub>                   | F3       | V <sub>DD33A</sub> |                    |

| A10        |                     | V <sub>SNSBOM</sub>                   | F4       | SHCLKA             |                    |

| A11        |                     | V <sub>SNSBOP</sub>                   | F5       |                    | SHCLK              |

| B1         | ASELA1              |                                       | F6       | GND                | GND                |

| B2         | ASELA0              |                                       | F7       | WPA                |                    |

| B3         |                     | ASELB1                                | F8       |                    | WPB                |

| B4         |                     | ASELB0                                | F9       |                    | V <sub>DD33B</sub> |

| B5         | GND                 | GND                                   | F10      |                    | FBB0               |

| B6         |                     | V <sub>CCB</sub>                      | F11      |                    | COMPB              |

| B7         | GND                 | GND                                   | G1       | COMPA0             |                    |

| B8         | RUNA0               |                                       | G2       | FBA0               |                    |

| B9         | RUNA1               |                                       | G3       | PGA0               |                    |

| B10        | nonai               | RUNBO                                 | G4       | PGA1               |                    |

| B10<br>B11 |                     | RUNB1                                 | G5       | GND                | GND                |

| C1         | SDA_A               |                                       | G6       | GND                | GND                |

| C2         | JDA_A               | SDA_B                                 | G7       |                    | PGB0               |

| C3         | GND                 | GND                                   | G8       |                    | PGB1               |

| C4         | PCFGA               |                                       | G9       |                    | FBB1               |

| C5         | FCFGA               |                                       | G10      |                    | COMPB              |

| C6         | GND                 | GND                                   | G11      |                    | COMPB              |

| C7         | GND                 | PCFGB                                 | H1       | CSA1M              | GOIVIED            |

| C8         |                     | VOB1CFG                               | H2       | IAVGA0             |                    |

| C9         | GND                 | GND                                   | H2<br>H3 | IAVGA0             |                    |

| C10        |                     | GND                                   | H4       | TSNSA1             |                    |

|            | SCL_A               |                                       |          |                    |                    |

| C11        |                     | SCL_B                                 | H5       | TSNSA0             |                    |

| D1         | FLTA1               |                                       | <u> </u> | VINSA              |                    |

| D2         | FLTAO               |                                       | H7       |                    | IAVGBO             |

| D3         |                     | FLTB1                                 | H8       |                    | IAVGB1             |

| D4         | 1/040050            | FLTBO                                 | H9       |                    | TSNSB              |

| D5         | VOA0CFG             | 0110                                  | H10      |                    | TSNSB              |

| D6         | GND                 | GND                                   | H11      | 00115              | PWMB               |

| D7         |                     | FCFGB                                 | J1       | CSA1P              |                    |

| D8         |                     | VOBOCFG                               | J2       | PWMA1              |                    |

| D9         | GND                 | GND                                   | J3       | CSAOM              |                    |

| D10        | SYNCA               |                                       | J4       | CSAOP              |                    |

| D11        |                     | SYNCB                                 | J5       | PWMA0              |                    |

| E1         | IAVGNDA             |                                       | J6       |                    | VINSB              |

| E2         | V <sub>DD25A</sub>  |                                       | J7       |                    | CSB1N              |

| E3         | VOA1CFG             |                                       | J8       |                    | CSB1P              |

| E4         | GND                 | GND                                   | J9       |                    | PWMB1              |

| E5         | GND                 | GND                                   | J10      |                    | CSBON              |

| E6         | GND                 | GND                                   | J11      |                    | CSBOP              |

## PIN FUNCTIONS

**COMP[A/B][1:0]:** Error Amplifier Outputs. PWM duty cycle increases with this control voltage. These are true low impedance outputs and cannot be directly connected together when active. For PolyPhase operation, wiring FB to  $V_{DD33}$  will three-state the error amplifier output of that channel, making it a slave. PolyPhase control is then implemented in part by connecting all slave COMP pins together to one master error amplifier output.

**TSNS[A/B][1:0]:** External Temperature Sense Inputs. The LTC7883 supports two methods of calculation of external temperature based on forward-biased P/N junctions between these pins and GND.

**VINS[A/B]:**  $V_{IN}$  Supply Sense. Connect to the  $V_{IN}$  power supply to provide line feedforward compensation. A change in  $V_{IN}$  immediately modulates the input to the PWM comparator and inversely changes the pulse width to provide excellent transient line regulation and fixed modulator voltage gain. An external lowpass filter can be added to this pin to prevent noisy signals from affecting the loop gain.

**IAVGND[A/B]:** IAVG Ground Reference. The same IAVGND should be shared between all channels of a PolyPhase rail and connected to system ground at a single point. IAVGND may be wired directly to GND on units that do not share phases with other units.

**PG[A/B][1:0]:** Power Good Indicator Open-Drain Outputs. These outputs are driven low through a 30µs filter when the respective channel output is below its programmed UV fault limit or above its programmed OV fault limit. If used, a pull-up resistor is required in the application. Operating voltage range is GND to V<sub>DD33</sub>.

**PWM[A/B][1:0]:** PWM Three-State Control Outputs. These pins provide single-wire PWM switching control for each channel to an external gate driver, DrMOS or power block. Operating voltage range is GND to V<sub>DD33</sub>.

**SYNC[A/B]:** External Clock Synchronization Input and Open-Drain Output. If desired, an external clock can be applied to this pin to synchronize the internal PWM channels. If an LTC7883 unit is configured as a clock master, this pin will also pull to ground at the selected

PWM switching frequency with a 125ns pulse width. A pull-up resistor to 3.3V is required in the application if SYNC is driven by any LTC7883. Minimize the capacitance on this line to ensure its time constant is fast enough for the application.

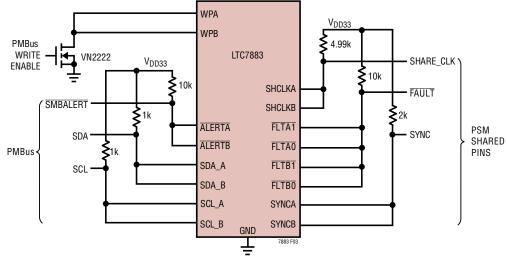

**SCL[A/B]:** Serial Bus Clock Input. A pull-up resistor to 3.3V is required in the application.

**SDA[A/B]:** Serial Bus Data Input and Output. A pull-up resistor to 3.3V is required in the application.

**ALERT[A/B]:** Open-Drain Status Output. This pin may be connected to the system SMBALERT wire-AND interrupt signal and should be left open if not used. If used, a pull-up resistor is required in the application. Operating voltage range is GND to V<sub>DD33</sub>.

**FLT[A/B][1:0]**: Programmable Digital Inputs and Open-Drain Outputs for Fault Sharing. Used for channel-to-channel fault communication and propagation. These pins should be left open if not used. If used, a pull-up resistor to 3.3V is required in the application.

**RUN[A/B][1:0]:** Run Control Inputs and Open-Drain Outputs. A voltage above 2V is required on these pins to enable the respective PWM channel. The LTC7883 will drive these pins low under certain reset/restart conditions regardless of any PMBus command settings. A pull-up resistor to 3.3V is required in the application.

**ASELA[1:0]:** Unit A Serial Bus Address Select Pins. Connect optional 1% resistor dividers between  $V_{DD25A}$  and GND to these pins to select the serial bus interface address.

**ASELB[1:0]:** Unit B Serial Bus Address Select Pins. Connect optional 1% resistor dividers between  $V_{DD25B}$  and GND to these pins to select the serial bus interface address.

**VO[A/B][1:0]CFG:** Output Voltage Configuration Pins. Connect optional 1% resistor dividers between  $V_{DD25}$ and GND to these pins to select the output voltage for each channel.

**FCFG[A/B]:** Frequency Configuration Pins. Connect an optional 1% resistor divider between  $V_{DD25}$  and GND to these pins to configure PWM switching frequency.

### PIN FUNCTIONS

**PCFG[A/B]:** Phase Configuration Pins. Connect an optional 1% resistor divider between  $V_{DD25}$  and GND to these pins to configure the phase of each PWM channel relative to SYNC.

$V_{DD25[A/B]}$ : Internal 2.5V Regulator Outputs. Bypass these pins to GND with a low ESR 1µF capacitor. Do not short these pins together or load them with external current beyond that required for local LTC7883 configuration.

**WP[A/B]:** Write Protect Inputs. If WP is above 2V, PMBus writes are restricted and any software WRITE\_PROTECT settings for that unit are overridden. These pins have an internal  $10\mu$ A pull-up to V<sub>DD33</sub>.

**SHCLK[A/B]:** Share Clock Open-Drain Outputs (bussed). Share Clock, nominally 100kHz, is used to sequence multiple rails in a power system utilizing more than one ADI PSM controller. A pull-up resistor is required in the application. Minimize the capacitance on this line to ensure the time constant is fast enough for the application. Operating voltage range is GND to  $V_{DD33}$ .

$V_{DD33[A/B]}$ : Internal 3.3V Regulator Outputs. Bypass these pins to GND with a low ESR 2.2µF capacitor. The LTC7883 may also be powered from an external 3.3V rail attached to these pins, if also shorted to  $V_{CC[A/B]}$ . Otherwise do not short these pins together or overload them with external system current. Local pull-up resistors for the LTC7883 itself may be powered from  $V_{DD33}$ .

$V_{CC[A/B]}$  (Pin 25): 3.3V Regulator Input(s). Bypass these pins, which may be shorted together, to GND with a capacitor (0.1µF to 1µF ceramic) in close proximity to the IC.

**V**<sub>SNS[A/B][1:0]M</sub>: Negative Output Voltage Sense Inputs. These pins must still be properly connected on slave channels for accurate output current telemetry.

**V**<sub>SNS[A/B][1:0]P</sub>: Positive Output Voltage Sense Inputs. These pins must still be properly connected on slave channels for accurate output current telemetry.

**CS[A/B][1:0]M:** Current Sense Amplifier Inputs. These (–) inputs to the amplifiers are normally connected to the low side of a DCR sensing network or output current sense resistor for each phase.

**CS[A/B][1:0]P:** Current Sense Amplifier Inputs. These (+) inputs are normally connected to the high side of an output current sense resistor or the R-C midpoint of a parallel DCR sense circuit for each phase.

**IAVG[A/B][1:0]:** Average Current Control Pins. A capacitor connected between these pins and IAVGND stores a voltage proportional to the average output current of the master channel. PolyPhase control is then implemented in part by connecting all slave IAVG pins together to the master IAVG output. This pin should be left open on channels that control single-phase outputs. Operating voltage range is GND to 2.1V.

**FB[A/B][1:0]:** Error Amplifier Inverting Inputs. These pins provide an internally scaled version of the output voltage for use in loop compensation.

**GND:** Ground. All GND balls must be soldered to a suitable PCB copper ground plane for proper electrical operation and to obtain the specified package thermal resistance.

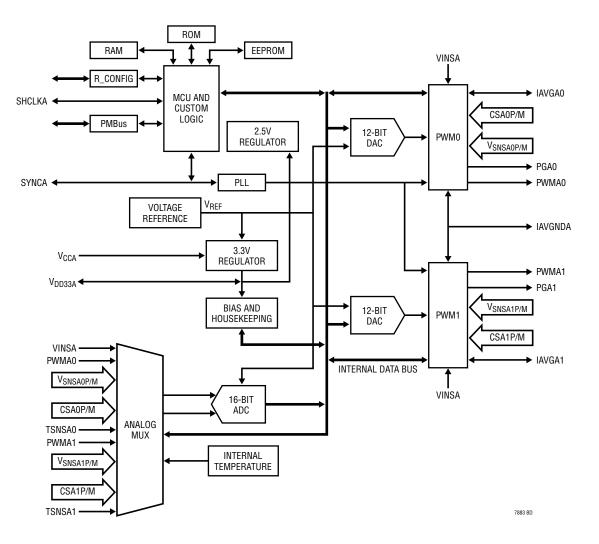

### BLOCK DIAGRAM ("A" Side, 1 of 2 Units)

### TEST CIRCUIT (Channel AO Example)

# TIMING DIAGRAM

# OPERATION

### Overview

The LTC7883 is a quad channel constant frequency analog voltage mode controller for DC/DC step-down applications. It features PMBus compliant digital interfaces for monitoring and control of important power system parameters. The IC operates from power supplies between 3V and 13.2V and is intended for conversion from V<sub>IN</sub> between 3V and 38V to output voltages between 0.1V and 5.25V. It is designed to be used in a switching architecture with external FET drivers, including higher level integrations such as non-isolated power blocks.

Major features include:

- Digitally Programmable Output Voltage, Current Limit and Related Supervisors

- Digitally Programmable Input Voltage Supervisor

- Digitally Programmable Switching Frequency with PLL for Synchronous PolyPhase Operation Up to 8 Phases

- Digitally Programmable On and Off Delay Times

- Digitally Programmable Soft-Start/Stop

- Operating Condition Telemetry

- Fully Differential Load Sense

- Nonvolatile Configuration Memory with ECC Capable of Standalone Operation

- Optional External Resistor Configuration of Key

Operating Parameters

- Optional Time-Base Interconnect for Synchronization Between Multiple Controllers

- Warning and Fault Status with Fault Event Data Logging

- PMBus Revision 1.2 Compliant Interface Up to 400kHz

#### **Internal Structure**

The LTC7883 is comprised of two dual-channel units, each equivalent to an LTC3882-1 with the added feature of a hardware PMBus write protect for each unit.

Refer to the LTC3882-1 data sheet for a detailed description of operation, PMBus command set, and applications information for each unit.

Refer to the LTC3888 data sheet for additional details on operation of the WP pins and their interaction with the PMBus WRITE\_PROTECT command on each unit.

#### **Unique Special ID**

Each internal unit of the LTC7883 reports a unique MFR\_ SPECIAL\_ID to differentiate it from an LTC3882-1. Table 1 lists MFR\_SPECIAL\_ID values for these products. X is adjustable by the manufacturer.

#### Table 1. MFR\_SPECIAL\_ID Values

| DEVICE         | MFR_SPECIAL_ID | MFR_MODEL |  |  |  |  |  |

|----------------|----------------|-----------|--|--|--|--|--|

| LTC3882-1      | 0x424X         | LTC3882-1 |  |  |  |  |  |

| LTC7883 Unit A | 0x450X         | LTC7883A  |  |  |  |  |  |

| LTC7883 Unit B | 0x451X         | LTC7883B  |  |  |  |  |  |

### OPERATION

#### Additional Identification Commands

The LTC7883 features a few new PMBus product identification commands as detailed in Table 2.

#### **Switching Frequency and Phase**

There is a high degree of flexibility for setting the PWM operating frequency of the LTC7883. The switching frequency of the PWM can be established with an internal oscillator or an external time base. The internal phaselocked loop (PLL) synchronizes PWM control to this timing reference with proper phase relation, whether the clock is provided internally or externally. The device can also be configured to provide the master clock to other ICs through PMBus command, EEPROM setting, or external configuration resistors as outlined in application Table 6. For PMBus or EEPROM configuration, an LTC7883 unit is designated as a clock master by clearing bit 4 of MFR\_CONFIG\_ALL\_LTC3882-1. As clock master, an LTC7883 unit will drive its open-drain SYNC pin at the selected rate with a pulse width of 125ns. An external pull-up resistor between SYNC and  $V_{DD33}$  is required in this case. Only one unit connected to SYNC should be designated to drive the pin. If more than one LTC7883 unit sharing SYNC is programmed as clock master, just one of the units is automatically elected to provide the clock. The others disable their SYNC outputs and indicate this with bit 10 of MFR\_PADS\_LTC3882-1.

Unlike the LTC3882-1, which only allows a fixed set of predetermined frequencies, the LTC7883 FREQUENCY\_SWITCH command supports a continuous range of values from 250kHz to 2.5MHz. The special case of 0x0000 for External SYNC Only is not permitted by the LTC7883. Sending this FREQUENCY\_SWITCH command value will result in a CML fault for invalid data.

The LTC7883 will automatically accept an external SYNC input, disabling is own SYNC drive if necessary, as long as the external clock frequency is greater than 1/2 of the programmed internal oscillator. Whether configured to drive SYNC or not, an LTC7883 unit can continue PWM operation at the selected frequency (FREQUENCY\_SWITCH) using its own internal oscillator if an expected external clock signal is not present.

The MFR\_PWM\_CONFIG\_LTC3882-1 command can be used to configure the phase of each channel. Desired phase can also be set from EEPROM or external configuration resistors as outlined in Table 6. Phase designates the relationship between the falling edge of SYNC and the internal clock edge that resets the PWM latch. That reset turns off the top power switch, producing a PWM falling edge. Additional small propagation delays to the PWM control pins will apply.

|               |          |                                 |          |       |             | DEFAUL   | T VALUE  |

|---------------|----------|---------------------------------|----------|-------|-------------|----------|----------|

| COMMAND NAME  | CMD CODE | DESCRIPTION                     | TYPE     | PAGED | DATA FORMAT | UNIT A   | UNIT B   |

| ID_DEVICE_ID  | 0xAD     | LTC7883 Model Number            | R String | Ν     | ASC         | LTC7883A | LTC7883B |

| ID_DEVICE_REV | 0xAE     | LTC7883 Device Revision<br>Code | R String | Ν     | ASC         | C0001    | C0001    |

#### **Table 2. New Identification Commands**

# OPERATION

The phase relationships and frequency are independent of each other, providing numerous application options. Multiple LTC7883 units/ICs can be synchronized to realize a PolyPhase array. In this case the phases should be separated by 360/n degrees, where n is the number of phases driving the output voltage rail.

### Serial Bus Addressing

The LTC7883 supports four types of serial bus addressing schemes to access the individual PWM channels separately or jointly.

- Global Bus Addressing

- Power Rail Addressing

- Individual Unit (Device) Addressing

- Page+ Channel Addressing

Each internal unit of the LTC7883 must be given a unique serial bus address for configuration and control. These units addresses can be derived from a combination of external configuration resistors attached to the ASEL

| Table 3. | Unique LTC7883 | <b>Default Factory</b> | EEPROM Values |

|----------|----------------|------------------------|---------------|

| 10010 01 | 0              | 2014411 1 40101 y      |               |

pins and PMBus command values stored in on-board EEPROM. This method of using ASEL pins to specify some or all of each unit's physical address is necessary when using default factory EEPROM programing, where both units are assigned to 0x4F. Applying external resistor configuration for unit addresses is recommended, as it allows for easier device recovery under a wide range of programming errors. Refer to the values in Table 7 for full details on setting each unit address.

### **Advanced Power Stages**

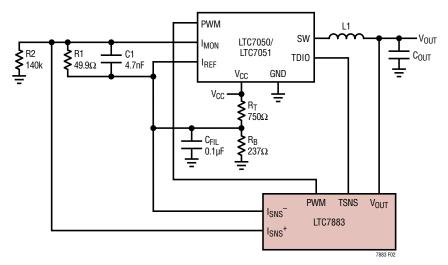

Some LTC7883 factory EEPROM defaults have been modified from LTC3882-1 values to better accommodate newer, advanced power stages that provide an output proportional to load current. Table 3 details these values. Refer to Figure 1 for an example of interfacing the LTC7883 to power stages or blocks of this type. If traditional DCR or discrete resistor sense of output current is used as shown on the front page, refer to factory EEPROM defaults given for Table 3 commands in the LTC3882-1 data sheet.

| COMMAND NAME         | CMD CODE | DESCRIPTION                                                | TYPE     | PAGED | DATA FORMAT | UNITS  | DEFAULT VALUE     |

|----------------------|----------|------------------------------------------------------------|----------|-------|-------------|--------|-------------------|

| IOUT_CAL_GAIN        | 0x38     | Ratio of I <sub>SENSE</sub> ± Voltage<br>to Sensed Current | R/W Word | Y     | L11         | mΩ     | 0.25mΩ<br>0xAA00  |

| IOUT_OC_FAULT_LIMIT  | 0x46     | Output Overcurrent Fault Limit                             | R/W Word | Y     | L11         | A      | 70.0A<br>0xEA30   |

| IOUT_OC_WARN_LIMIT   | 0x4A     | Output Overcurrent Warning Limit                           | R/W Word | Y     | L11         | A      | 50.0A<br>0xE320   |

| MFR_IOUT_CAL_GAIN_TC | 0xF6     | Output Current Sense Element<br>Temperature Coefficient    | R/W Word | Y     | CF          | ppm/°C | 0ppm/°C<br>0x0000 |

#### Using FREQUENCY\_SWITCH

Each unit in the LTC7883 that is a clock slave should have FREQUENCY\_SWITCH programmed to the same value as its clock master, whether another LTC7883 or not. In the case where external synchronization will be used to control the shared SYNC line, each LTC7883 should be programmed with a value of FREQUENCY\_SWITCH that is as close to the external clock frequency as possible.

#### **Resistor Configuration Pins**

Like the LTC3882-1, each LTC7883 unit is programmed to use external resistor configuration by factory default. This allows output voltage, PWM frequency and phasing, and the PMBus address to be set without programming the part through its serial interface or purchasing devices with custom EEPROM contents. The RCONFIG pins all require a resistor divider between V<sub>DD25</sub> and GND. The RCONFIG pins are only interrogated at initial power-up and during a reset, so modifying their values on-the-fly is not recommended. RCONFIG pins on the same unit can share a single resistor divider if they require identical programming, but these dividers should not be shared across different LTC7883 units. Resistors with a tolerance of 1% or better must be used to assure proper operation. In Table 4 through Table 6, R<sub>TOP</sub> is connected between VDD25 and the RCONFIG pin, while RBOT is connected between the pin and GND. Noisy clock signals should not be routed near these pins.

RCONFIG address selection for each LTC7883 unit follows the values given in Table 7 of this data sheet.

Output voltage can be set as shown in Table 4. For example, setting  $R_{TOP}$  to 16.2k $\Omega$  and  $R_{BOT}$  to 17.4k $\Omega$  is equivalent to programming a VOUT\_COMMAND value of 1.8V. Refer to the Operation section of the LTC3882-1 data sheet for related parameters that are also automatically set as a percentage of the programmed  $V_{OUT}$  if resistor configuration pins are used to determined output voltage.

Operating PWM frequency can be set as shown in Table 5. Note that if SYNC pins are shared between LTC7883 units, all those units should be programmed to the same frequency, but only one SYNC output should be enabled. All other SYNC outputs should be disabled. Refer to the following PCFG discussion for additional details on controlling SYNC output enable with external programming resistors.

| $R_{TOP}$ (k $\Omega$ ) | R <sub>B0T</sub> (kΩ) | V <sub>OUT</sub> (V)                          |

|-------------------------|-----------------------|-----------------------------------------------|

| 0 or Open               | Open                  | From EEPROM                                   |

| 10                      | 23.2                  | 5.0                                           |

| 10                      | 15.8                  | 3.3                                           |

| 16.2                    | 20.5                  | 2.5                                           |

| 16.2                    | 17.4                  | 1.8                                           |

| 20                      | 17.8                  | 1.5                                           |

| 20                      | 15                    | 1.35                                          |

| 20                      | 12.7                  | 1.25                                          |

| 20                      | 11                    | 1.2                                           |

| 24.9                    | 11.3                  | 1.15                                          |

| 24.9                    | 9.09                  | 1.1                                           |

| 24.9                    | 7.32                  | 1.0                                           |

| 24.9                    | 5.76                  | 0.9                                           |

| 24.9                    | 4.32                  | 0.75                                          |

| 30.1                    | 3.57                  | 0.65                                          |

| 30.1                    | 1.96                  | 0.6                                           |

| Open                    | 0                     | Output OFF*<br>(V <sub>OUT</sub> from EEPROM) |

\*OPERATION value and RUN*n* pin must both command the channel to start from this configuration.

#### Table 5. FCFGA/B Resistor Programming

| R <sub>TOP</sub> (kΩ) | R <sub>B0T</sub> (kΩ) | SWITCHING<br>Frequency (kHz) |

|-----------------------|-----------------------|------------------------------|

| 0 or Open             | Open                  | From EEPROM                  |

| 10                    | 23.2                  | 2500                         |

| 10                    | 15.8                  | 2250                         |

| 16.2                  | 20.5                  | 2000                         |

| 16.2                  | 17.4                  | 1750                         |

| 20                    | 17.8                  | 1500                         |

| 20                    | 15                    | 1250                         |

| 20                    | 12.7                  | 1000                         |

| 20                    | 11                    | 900                          |

| 24.9                  | 11.3                  | 750                          |

| 24.9                  | 9.09                  | 600                          |

| 24.9                  | 7.32                  | 500                          |

| 24.9                  | 5.76                  | 450                          |

| 24.9                  | 4.32                  | 400                          |

| 30.1                  | 3.57                  | 350                          |

| 30.1                  | 1.96                  | 300                          |

| Open                  | 0                     | 250                          |

Table 6 shows various PWM phase configurations that can be selected with external resistor programming. This RCONFIG pin, as with the LTC3882-1, can also be used to control SYNC output drive for each LTC7883 unit. However, there are more choices here, affording greater flexibility in PolyPhase configurations.

For example, to build a four-phase rail, one approach might be to select  $R_{TOP}$  of 24.9k $\Omega$  and  $R_{BOT}$  of 5.76k $\Omega$  for PHAS\_CFG of Unit A (PCFGA). This programs the phase angles of PWMA0 to 0° and PWMA1 to 180°, relative to the falling edge of SYNC. Unit A is enabled to drive the shared SYNC clock line through the SYNCA pin (opendrain output).

For Unit B,  $R_{TOP}$  of  $10k\Omega$  and  $R_{BOT}$  of  $15.8k\Omega$  selects phase angles for PWMB0 of 90° and PWMB1 of 270°, configuring SYNCB as an input to accept the master clock from Unit A. The result, when wired as a 4-phase rail as described in PolyPhase Operation and Load Sharing under Applications Information in the LTC3882-1 data sheet, will be four non-overlapping phases operating in quadrature as desired. In this case, either Unit A or Unit B may be defined and wired as the voltage loop master, since this function is independent of clock mastering.

Only mix phase selections on PolyPhase rails that have the same maximum duty cycle specified in Table 6.

| R <sub>TOP</sub> (kΩ) | R <sub>BOT</sub> (kΩ) | θ <sub>sync</sub> to θ <sub>o</sub> | θ <sub>SYNC</sub> TO θ <sub>1</sub> | MAXIMUM DUTY CYCLE | SYNC OUTPUT DISABLED |  |

|-----------------------|-----------------------|-------------------------------------|-------------------------------------|--------------------|----------------------|--|

| 0 or Open             | Open                  | From EEPROM                         | From EEPROM                         | See MFR_PWM_CONFIG | From EEPROM          |  |